# تصميم النظم المنطقية باستخدام الدارات المنطقية المبرمجة

المحاضرة الأولى

د.م. خولة حموي khawla.hamwi@gmail.com

العام الدراسي: 2023-2024

## عناوين المحاضرة

- •تمثيل النظام الرقمي

- •تصنيف الأنظمة الرقمية

- •النظم المنطقية المبرمجة

- تصنيف النظم المنطقية المبرمجة

- الأجهزة المنطقية المبرمجة البسيطة

- الأجهزة المنطقية المعقدة

- •أجهزة الـ FPGA

- فوائد مساوئ الـ FPGA

- ميزات متقدمة لأجهزة الـ FPGA

- •منهجية التصميم باستخدام تقنية FPGA

# تمثيل النظام الرقمي (1/4)

أصبح تصميم الأنظمة الرقمية معقداً جداً مما استوجب تقسيم عملية التصميم إلى عدة مهام انطلاقاً من خصائص النظام وصولاً إلى التصميم الفيزيائي.

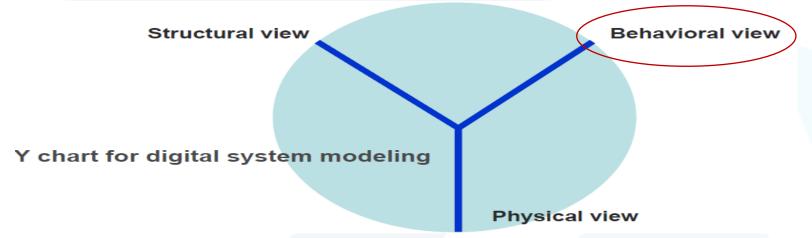

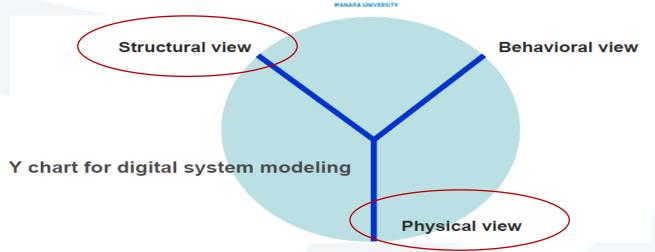

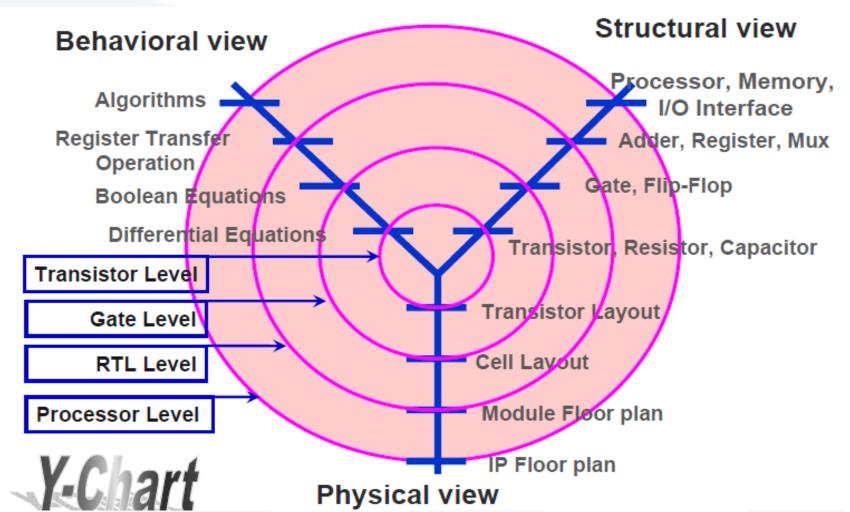

يوجد ثلاث منظورات Views لوصف النظام الرقمي كما هو مبين في الشكل:

1. المنظور السلوكي Behavioral view: يسمى أحياناً بالمستوى الوظيفي أو مستوى الخصائص حيث يصف وظيفة أو سلوك النظام ويتعامل مع النظام كصندوق أسود بغض النظر عن البنية الداخلية للنظام.

لا توجد صيغة واحدة لوصف النظام سلوكياً إنما توجد عدة طرائق كالمعادلات التفاضلية أو جداول الحقيقة أو مجموعة تعليمات المعالج أوبشكل خوارزمية تصف العلاقة بين إشارة الدخل وإشارة الخرج.

## تمثيل النظام الرقمي (2/4)

2. المنظور البنيوي: يصف هذا المنظور البنية الداخلية للنظام ويظهر بوضوح مكونات النظام الداخلية وكيفية ربط هذه المكونات مع بعضها البعض.

يعبر هذا المنظور عن مخطط النظام الداخلي system diagram

3. المنظور الفيزيائي: يصف الخصائص الفيزيائية للنظام، ويضيف معلومات تفصيلية عن النظام إلى المنظور البنيوي. يحدد هذا المنظور العجم الفيزيائي للعناصر

والتوضع الفيزيائي للعناصر على اللوحة Board أوالرقاقة السيليكونية

يقدم المنظور الفيزيائي معلومات تفصيلية عن النظام أكثر من المنظورين السابقين ولكن يحتاج في الوقت نفسه إلى زمن أطول في عملية المحاكاة

## تمثيل النظام الرقمي (3/4)

- أصبحت كثافة الشريحة في الوقت الراهن عالية جداً بحيث أصبحت تحتوي ملايين الترانزستورات على الشريحة نفسها.

- لإدارة درجة التعقيد هذه تم اقتراح وصف النظام على عدة مستويات تجريدية حيث هدف المستوى التجريدي إلى تخفيض كمية المعطيات لمستوى قابل للإدارة.

- و يحتوي المستوى التجريدي الأعلى High level abstraction على معظم المعلومات الاساسية لوصف النظام في حين يحتوي المستوى التجريدي الأقل Low level abstraction معلومات تفصيلية أكثر من باقي المستويات التجريدية الأعلى.

- يقسم النظام الرقمي وفق كل منظور إلى أربعة مستويات تجريدية:

- مستوى الترانزستور Transistor level.

- مستوى البوابات المنطقية Gate level.

- Register transfer level (RTL) مستوى نقل المسجلات

- مستوى النظام System level أو مستوى المعالج Processor level.

# تمثيل النظام الرقمي (4/4)

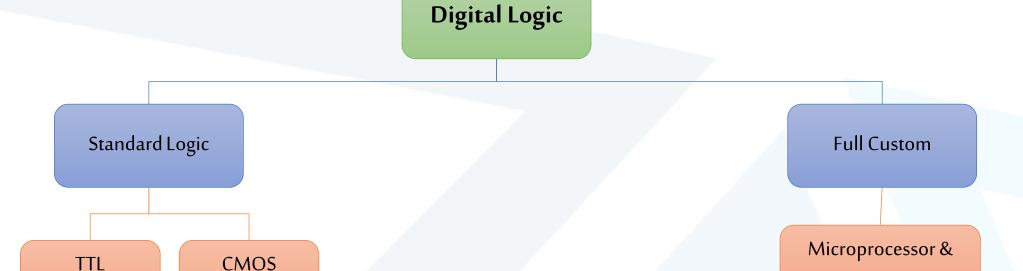

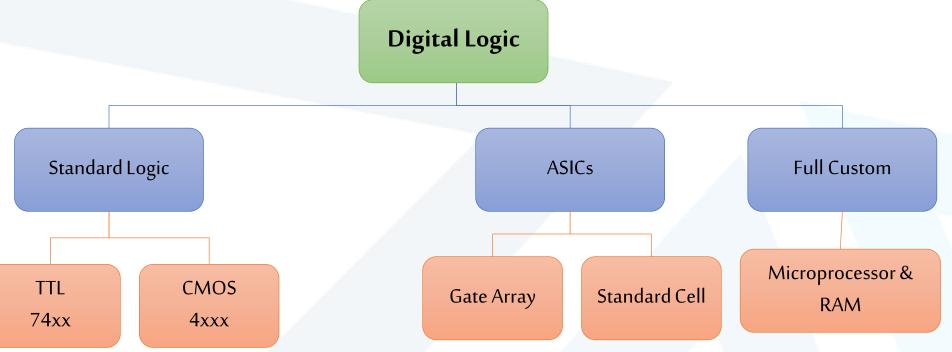

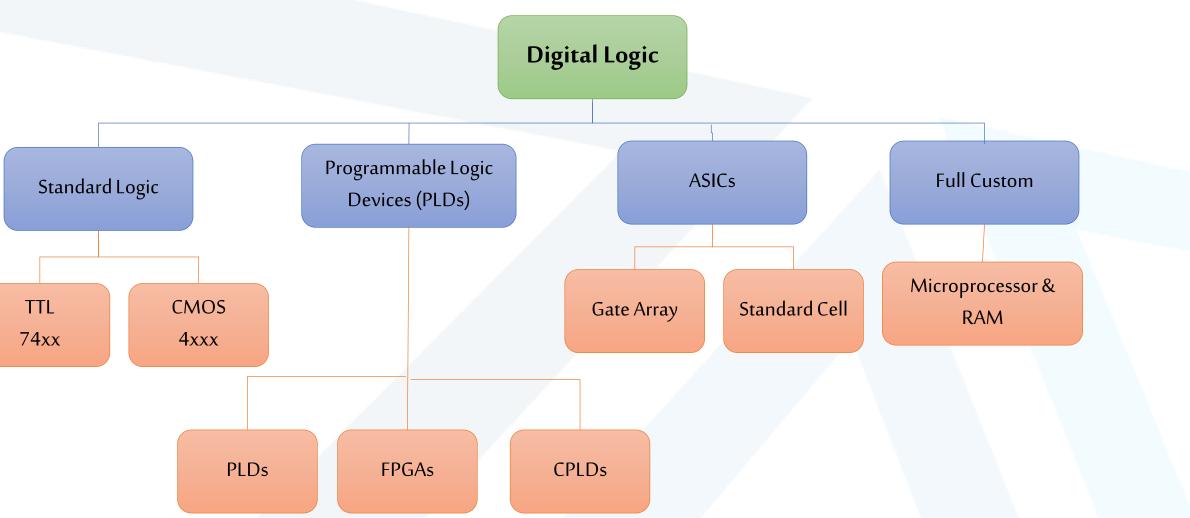

#### تصنيف الأنظمة الرقمية (1/3)

النظم الرقمية التي تستخدم المنطق المعياري standard logic كالأنظمة التي تستخدم تقنيات TTLو CMOS لإنجاز هذه الأنظمة

4xxx

74xx

دارات Full Custom للأغراض العامة purpose للأغراض العامة Full Custom للأغراض العامة كبيرة كالمعالجات microprocessor والذواكر

**RAM**

#### تصنيف الأنظمة الرقمية (2/3)

الدارات المتكاملة للتطبيقات الخاصة Application Specific Integrated Circuits ASICs، والتي تستخدم تقنيات خاصة لإنجازها كالخلايا المعيارية Application Specific Integrated Circuits ASICs ومصفوفة البوابات Gate arrays

# تصنيف الأنظمة الرقمية (3/3)

#### النظم المنطقية المبرمجة (PLDs) النظم المنطقية المبرمجة

- •تحتوي الدارات المنطقية المبرمجة على خلايا منطقية رقمية digital logic cells وشبكة ربط مبرمجة

- •تتلخص الفكرة الأساسية لهذه الدارات بإمكانية المصمم الرقمي على قابلية تشكيل هذه الخلايا المنطقية وبرمجة شبكة الربط لبناء دارة الكترونية رقمية بوظيفة محددة

- •تشبه هذه الدارات بطريقة برمجتها المتحكمات الصغرية والذواكرالقابلة للبرمجة، لكن مع تطور تقنية الدارات الرقمية المبرمجة، أصبح لهذه الدارات إمكانيات أوسع من المتحكمات الصغرية.

- •تختلف هذه الدارات عن الأنظمة الرقمية المسبقة التصميم وفق وظيفة معينة، حيث تسمح هذه الدارات للمصمم ببرمجها وفق الوظيفة الرقمية المرغوبة

من أجل التطبيقات التي تحتاج مجموعة صغيرة من الخلايا المنطقية، فإن الخيار يقع على الدارات الرقمية ذات الوظيفة الثابتة والمعرفة مسبقاً، أما بالنسبة للتطبيقات المعقدة (كالمرشحات الرقمية) فإن الخيار يقع على النظم الرقمية القابلة للبرمجة

## تصنيف النظم المنطقية المبرمجة (1/2)

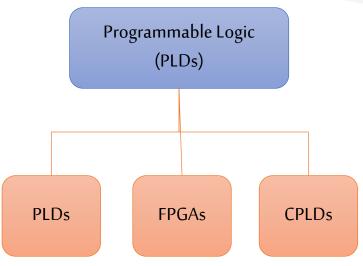

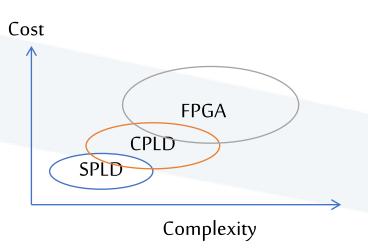

يوجد ثلاثة أصناف للنظم أو الأجهزة الرقمية المبرمجة:

• الأجهزة الرقمية المبرمجة البسيطة Simple Programmable Logic Devices SPLD، وتعرف اختصاراً بأجهزة PLD وتعرف اختصاراً بأجهزة الأجهزة الرقمية المبرمجة البسيطة والقلابات المنطقية والقلابات التي يمكن تشكيلها (برمجتها) لتؤدي الوظيفة المرغوبة

• الأجهزة الرقمية المبرمجة المعقدة Complex Programmable Logic Devices CPLD. تتألف هذه الأجهزة من مجموعة من الأجهزة DLD

•مصفوفة البوابات الحقلية القابلة للبرمجة Field Programmable Gate Array FPGA. تتألف من بنية رقمية معقدة تسمح بتصميم الأنظمة الرقمية المعقدة

#### تصنيف النظم المنطقية المبرمجة (2/2)

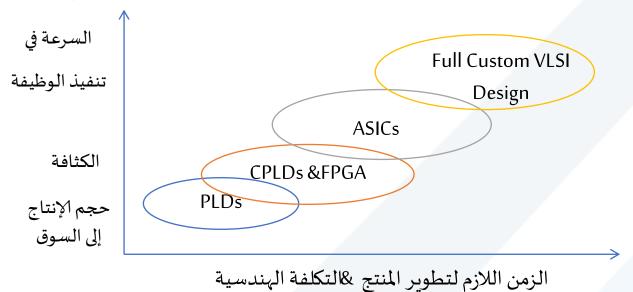

تصنف الأنظمة الرقمية من حيث الكثافة (التي تتحدد من خلال عدد الترانزستورات أو البوابات المنطقية في الشريحة الواحدة) إلى SSI, MSI, LSI, VLSI

تستخدم أجهزة PLD لتصميم الأنظمة الرقمية الصغيرة Small Scale integrated Circuits SSI والأنظمة الرقمية المتوسطة Very Large Scale integrated Circuits VLSI والكبيرة جداً Large Scale integrated Circuits LSI فيمكن استخدام

الأجهزة CPLD وFPGA.

تختلف هذه الأصناف عن بعضها البعض من حيث السرعة Speed والكثافة density والتكلفة cost ومجال التطبيق.

يمكن مقارنة الأجهزة الرقمية المبرمجة بنوعها البسيط PLD والمعقد CPLD,FPGA مع الأنظمة الرقمية المسممة للأغراض الخاصة ASIC والأنظمة الرقمية المسممة للأغراض العامة Full Custom

# الأجهزة المنطقية المبرمجة البسيطة SPLD (1/3)

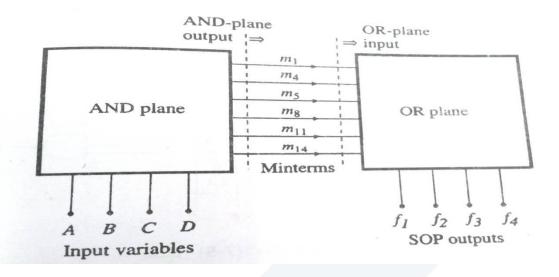

•تتألف هذه الأجهزة من مصفوفتين: مصفوفة البوابات المنطقية AND ومصفوفة البوابات المنطقية OR التي يمكن برمجها لتحقيق وظيفة منطقية محددة.

• المصفوفة القابلة للبرمجة عبارة عن شبكة من التوصيلات التي تشكل الأسطر والأعمدة، توجد منصهرة Fuse عن كل نقطة تقاطع (سطر مع عمود).

• باستخدام المصفوفة AND والمصفوفة OR يمكن تشكيل الأجهزة الرقمية القابلة للبرمجة PLD.

• تطبق متغيرات الدخل على المصفوفة AND للحصول على الحدود الأصغرية تطبق متغيرات الدخل على المصفوفة AND ومن ثم تطبق الحدود الأصغرية كمداخل المصفوفة OR للحصول على مجموع الجداءات (SOP) المتمثلة fi بالتوابع المنطقية

# الأجهزة المنطقية المبرمجة البسيطة 2/3)SPLD

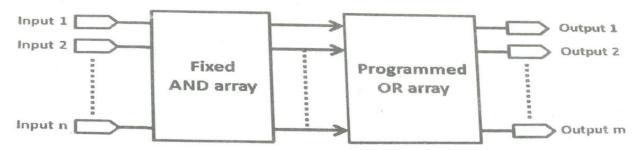

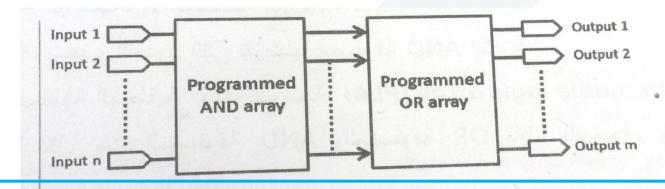

تصنف أجهزة PLD إلى أربعة أنواع:

1. ذاكرة القراءة فقط (Programmed Read-only Memory (PROM: تتألف من مصفوفة AND مبرمجة مسبقاً بشكل مثبت تعمل كمرمز، ومصفوفة

OR قابلة للبرمجة. لا تستخدم PROM كأجهزة قابلة للبرمجة إنما كذاكرة عنونة وذلك بسبب الحدود التي تفرضها مصفوفة AND الثابتة.

2. المصفوفة المنطقية القابلة للبرمجة (Programmable Logic Array (PLA: يكون فيها كل من المصفوفة AND والمصفوفة OR قابلة للبرمجة. وتستخدم لتجاوز

المحدودية في PROM

# الأجهزة المنطقية المبرمجة البسيطة SPLD (3/3)

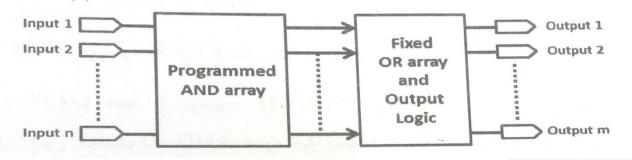

3. المنطق المصفوفي القابل للبرمجة (PAL) Programmable Array Logic (PAL؛ تتألف من مصفوفة AND القابلة للبرمجة ومصفوفة OR الموصولة مسبقاً بشكل ثابت. تستخدم لتجاوز المحدودية في أجهزة PLA كدرجة التعقيد الكبير نسبياً وكزمن التأخير الطويل. يضاف إلى المصفوفتين دارات منطقية خاصة بالخرج. يمكن لهذه الأجهزة تحقيق أي وظيفة منطقية يمكن التعبير عنها بصيغة مجموع الجداءات SOP.

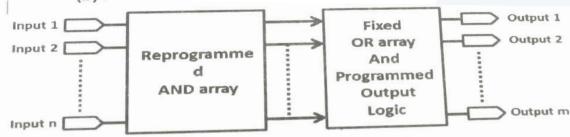

4. المنطق المصفوفي العام (Generic Array Logic (GAL: وهي الأجهزة الأحدث ضمن أجهزة PLD، يتألف من مصفوفة AND القابلة للبرمجة ومصفوفة

الثابتة ودارات منطقية للخرج قابلة للبرمجة.

## الأجهزة المنطقية المبرمجة المعقدة CPLD

#### تتألف هذه الأجهزة من:

- 1. مصفوفة من الأجهزة الرقمية البسيطة SPLD تتوضع على شريحة واحدة. يشكل جهاز الـ PLD **الكتلة الوظيفية** وهي عبارة عن أجهزة رقمية قابلة للبرمجة مثل PAL أو GAL

- أ. شبكة التوصيلات التي تربط الكتل الوظيفية PAL وهي قابلة للبرمجة

- وحدة الدخل/الخرج وهي بدورها قابلة للبرمجة لتشكيل خيارات متعددة من حالات الدخل والخرج

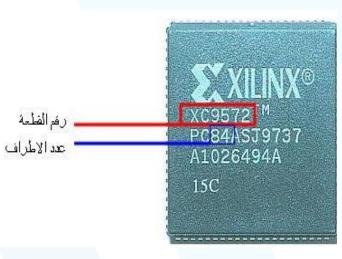

| العائلات                              | الشركة  |

|---------------------------------------|---------|

| MAX 7000, MAX 9000, and FLEX families | Altera  |

| XC9500 and Coolrunner family          | Xilinx  |

| ATF and ATV families                  | Atmel   |

| ispLSI family and MACH family         | Lattice |

يوجد العديد من الشركات العالمية المنتجة لهذه الأجهزة وبأنواع مختلفة. تنتج هذه الأجهزة على شكل سلسلة من العائلات تختلف من حيث الكثافة (عدد الكتل الوظيفية على الشريحة الواحدة) والأداء واستهلاك الاستطاعة وجهد التغذية والسرعة وتكنولوجيا التصنيع والتكلفة.

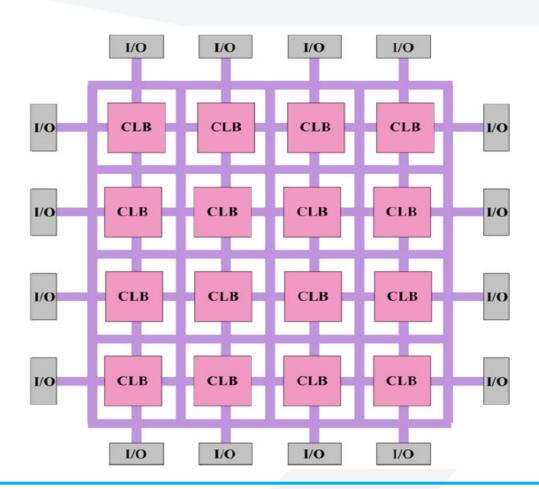

## أجهزة الـ 1/4)FPGA(1/4)

•تم تطوير هذه الأجهزة بشكل مختلف عن أجهزة CPLD، فالكتل الوظيفية لا تعتمد على تقنية PAL أو GAL، إنما تعتمد على كتل منطقية قابلة للتشكيل

.configurable logic block CLB

• تمتلك هذه الأجهزة درجة كثافة density أكبر من أجهزة CPLD ويمكن استخدامها لتطبيقات أكثر تعقيداً.

•تعتمد هذه الأجهزة على تقنية Look Up Table LUT التي تصنع بوساطة ذواكر SRAM.

• الكتل الوظيفية CLB أقل تعقيداً من الكتل الوظيفية في أجهزة CPLD لكنها أكثر عدداً وتكلفتها أعلى من تكلفة أجهزة CPLD

# أجهزة الـ (2/4)FPGA)

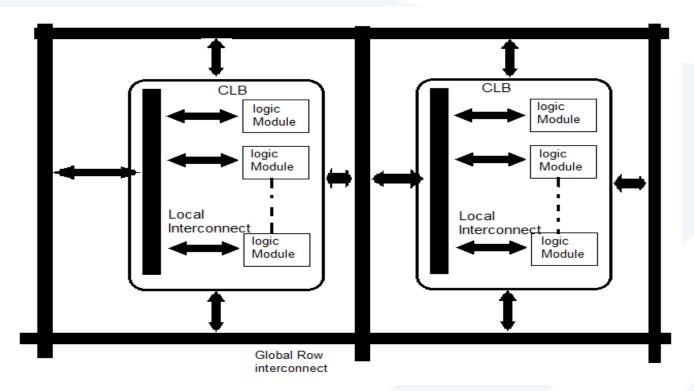

• يتألف كل CLB من عدة وحدات منطقية Logic Module تحتوي على شبكة ربط محلية على شكل أسطر وأعمدة لربط هذه الوحدات مع بعضها ومع CLB الأخرى.

• تتألف الوحدة المنطقية من الجدول LUT ودارات منطقية (كالقلابات) لبرمجة هذه الوحدة في المنطق التركيبي والمنطق التتابعي أوكليهما

•تصنف أجهزة FPGA إلى nonvolatile أو volatile.

في الحالة الأولى يفقد CLB معطيات البرمجة عند انقطاع التغذية الكهربائية. لذلك تدمج ذاكرة nonvolatile SRAM قابلة للبرمجة ضمن شريحة FPGA بحيث تخزن معطيات البرمجة على هذه الذاكرة وتكون قادرة على برمجة CLB عند عودة التغذية الكهربائية

## أجهزة الـ (3/4) (3/4)

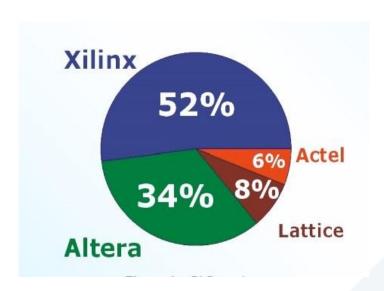

•تنتج الشركات عدة عائلات تختلف عن بعضها البعض من حيث الكثافة واستهلاك الاستطاعة والسرعة والتكلفة وجهد التغذية.

#### Xilinx: XC4000, Spartan, and Virtex Family

## أجهزة الـ (4/4) (4/4)

•تنتج الشركات عدة عائلات تختلف عن بعضها البعض من حيث الكثافة واستهلاك الاستطاعة والسرعة والتكلفة وجهد التغذية.

#### ALTERA: FLEX, Cyclone, and Stratix Family

#### فوائد ومساوئ ال FPGA

#### المساوئ

- •FPGA أبطأ من ASIC

- غير مؤمثلة بالنسبة لاستهلاك الطاقة

- •برمجها ليست سهلة

- •معقدة نوعاً ما

#### الفوائد

- •هذه الأجهزة مناسبة للتنفيذ السريع للدارات الرقمية

- •سهلة الاستجابة للتعديلات كما في حالة التعديلات البرمجية

- كثافة عالية لتنفيذ التوابع المنطقية المعقدة

- •أداء عالي في معالجة البيانات تفرعياً

- كلفة منخفضة

- •برمجة سريعة

## ميزات متقدمة لأجهزة FPGA

- •قام مصممو تقنية FPGA بإضافة دارات خاصة إلى شريحة FPGA كي تواكب تطورات الأنظمة الرقمية مما ساعد في استخدام هذه الشرائح في كثر من التطبيقات التي تتطلب أداء عالياً كالوسائط المتعددة وتشفير المعلومات. تتضمن هذه الإضافات:

- 1. نواة معالجات صغرية.على سبيل المثال تستخدم شركة Xilinx المعالج الرقمي PowerPC بينما تستخدم Altera معالج يسمى Niosll

- 2. مرسلات ومستقبلات في تطبيقات الاتصالات الرقمية والشبكات الحاسوبية

- 3. وحدات حسابية

- 4. معالجات الإشارة الرقمية DSP

- 5. وحدات تخزبن

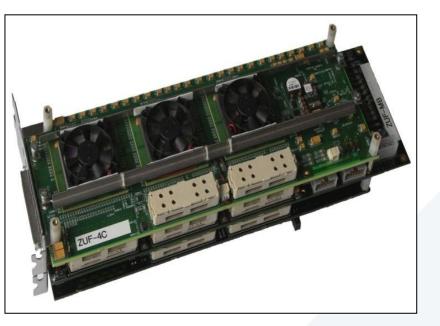

Zebu UF4 plateform (4 FPGA Virtex4)

Zebu server(100 FPGA Virtex5)

تسمى هذه الشرائح بعد عملية الإضافة FPGA Platform

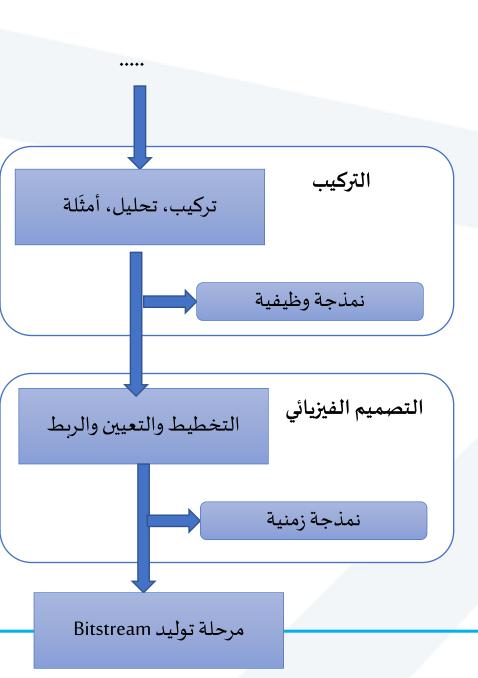

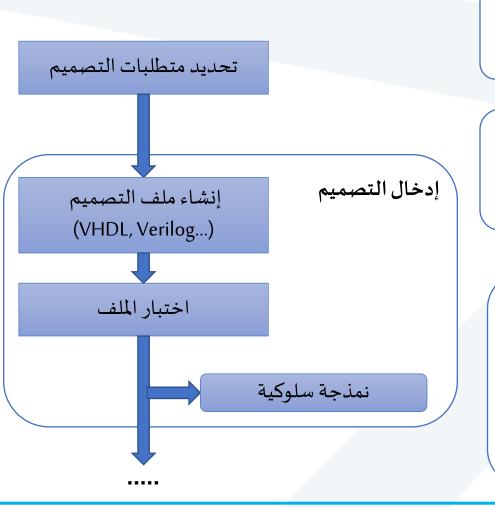

## منهجية التصميم باستخدام تقنية FPGA

يتم في المرحلة الأولى تعريف الوظائف التفصيلية للنظام المطلوب تصميمه بالإضافة إلى تحديد بعض البارامترات المهمة للنظام كالأداء performance

يتم في هذه المرحلة اختيار تكنولوجيا التنفيذ واختيار العناصر والأدوات البرمجية المستخدمة في عمليات التصميم.

يتم في هذه المرحلة إدخال التصميم باستخدام لغات وصف العتاد الصلب HDL (VHDL) كما يمكن إدخال التصميم باستخدام لغات أخرى مثل ++C/C وتوليد أو ترجمة التصميم إلى شيفرة مكتوبة بإحدى لغات وصف العتاد الصلب على مستوى RTL وهو ما يسمى تقنية التركيب عالي المستوى High Level Synthesis) HLS

# منهجية التصميم باستخدام تقنية FPGA

تساهم مرحلة التركيب في تحويل الشيفرة المكتوبة بلغات وصف العتاد الصلب إلى شبكة ربط من البوابات المنطقية موجهة للتنفيذ على أجهزة FPGA

تتضمن مرحلة التصميم الفيزيائي تحويل التصميم من منظوره البنيوي إلى المنظور الفيزيائي. تتألف من عدة مراحل جزئية ( التخطيط Floorplan والتعيين placement )

تتضمن مرحلة توليد Bitstream توليد الملفات التنفيذية التي تبرمج من خلالها الأجهزة الرقمية القابلة للبرمجة FPGA