## •

### البنيان Architecture

## I/O System Design معالجات صغرية تصميم نظام الدخل/الخرج

- □ 65,536 بوابة دخل خرج

- □ نقل البيانات من وإلى المعالج عن طريق باص البيانات data bus

- □ استخدام باص العناوين [15:0] A لتحديد عنوان البوابة

- □ المسجل AL (أو AX)يستقبل بيانات الدخل أويقدم بيانات الخرج

####

Address bus A[15:0]

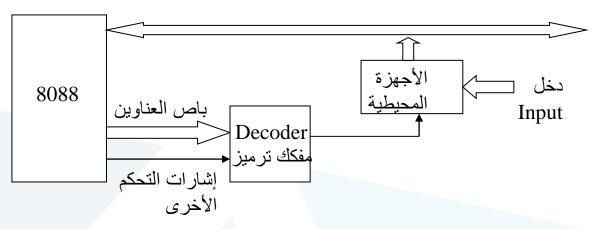

- تستخدم أجهزة I/O لتحقيق هدفين أساسيين:

- الاتصال بالعالم الخارجي

- لتخزين البيانات data.

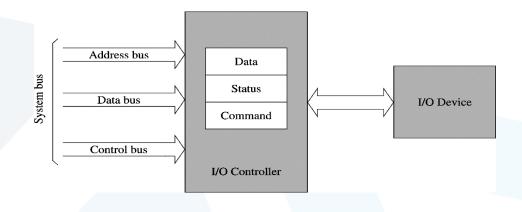

- تعمل متحكمات I/O كواجهة ملاءمة بينية تتوسط باص النظام systems bus وأجهزة الـ I/O .

- تحرر المعالج من الاهتمام بالتفاصيل الداراتية المتعلقة بهذه الأجهزة.

- \_ تهتم بالملاءمة الداراتية.

- لمتحكمات الـI/O ثلاثة أنواع من المسجلات:

- Data بيانات –

- أمر Command

- Status —

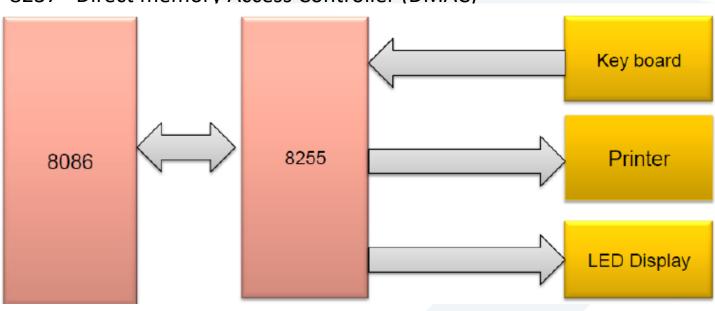

Intel has developed several peripheral control chips for 80x86 family

-provide complete I/O interface to x86 chip

Other Peripheral Devices

8253/8254 – Programmable Interval Timer (PIT)

8259 – Programmable Interrupt Controller (PIC)

8237 – Direct memory Access Controller (DMAC)

# الوحدات المحيطية Microprocessors and الوحدات المحيطية Interfaces

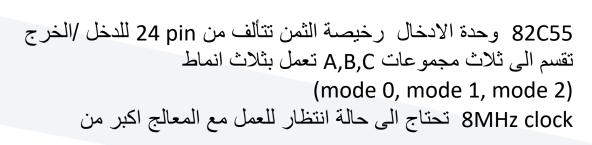

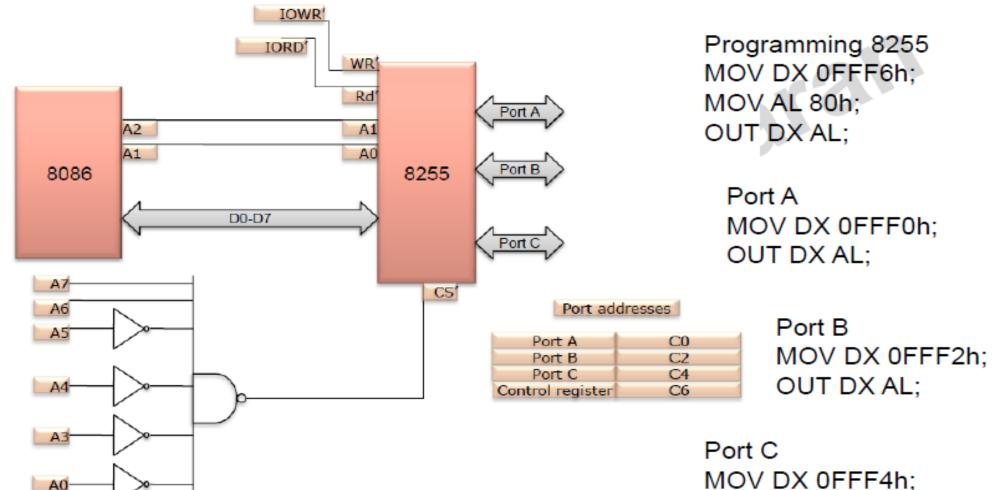

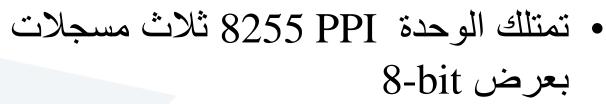

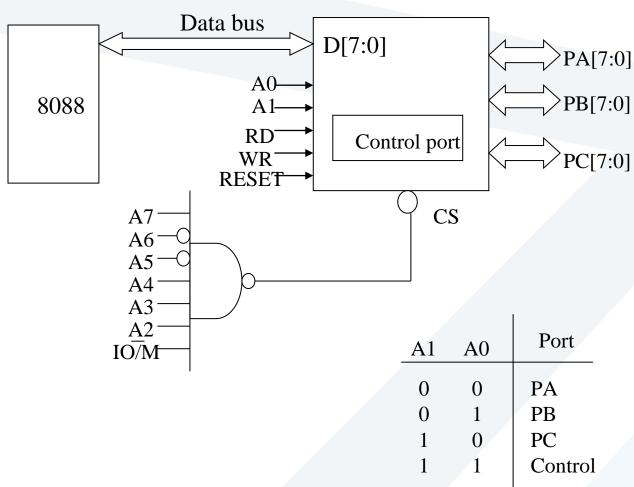

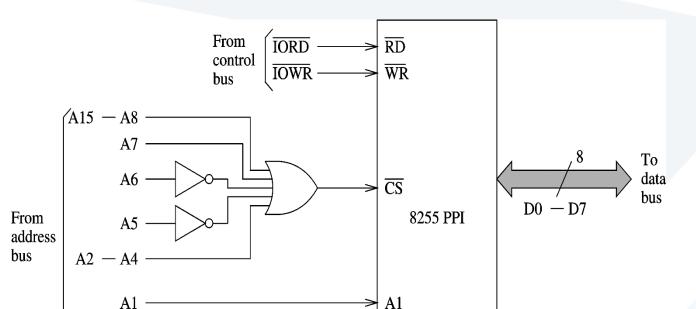

8255 Programmable Peripheral Interface

PPI 8055 وحدة مزودة بثلاث بوابات ادخال كال منها من 8 bit على نفس الشريحة تتصل مباشرة مع المعالج 8086

## الوحدات المحيطية

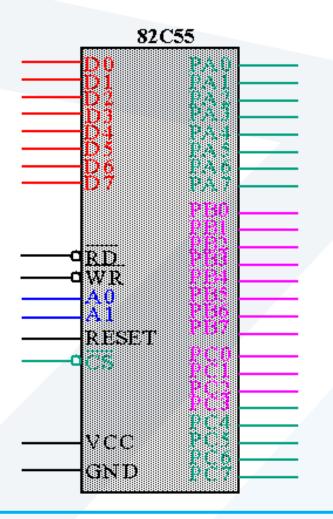

## Pin Diagram of 8255

## الوحدات المحيطية

| CS' | $\mathbf{A}_1$ | <b>A</b> <sub>o</sub> | Selected          |  |  |

|-----|----------------|-----------------------|-------------------|--|--|

| 0   | 0              | 0                     | Port A            |  |  |

| o   | o              | 1                     | Port B            |  |  |

| 0   | 1              | 0                     | Port C            |  |  |

| o   | 1              | 1                     | Control Register  |  |  |

| 1   | х              | х                     | 8255 Not Selected |  |  |

**Selecting Port / Programming 8255**

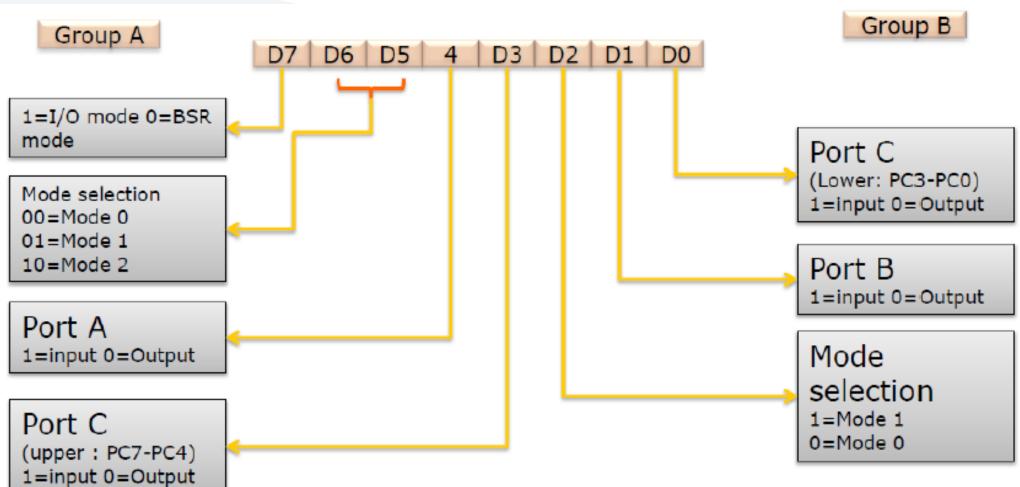

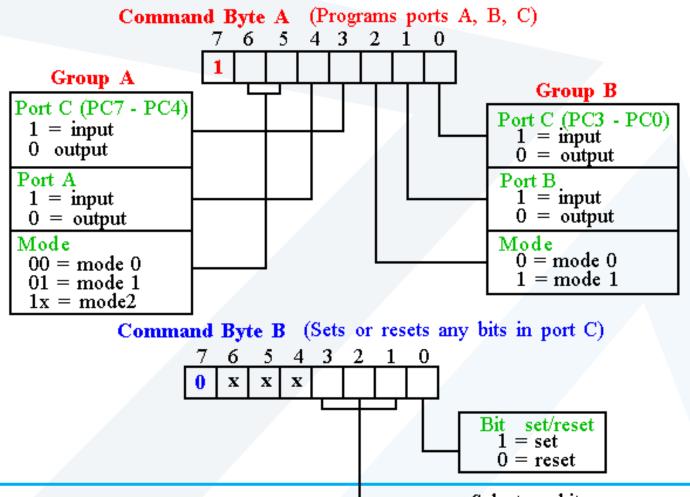

#### Control word Format

## Control word Format

| $D_7$                          | $D_6$        | $\mathrm{D}_5$ | $D_4$                         | $D_3$           | $D_2$                             | $D_{i}$ | $D_{o}$            |

|--------------------------------|--------------|----------------|-------------------------------|-----------------|-----------------------------------|---------|--------------------|

|                                | o 1 - Mode 1 |                | Port A                        | Port C<br>Upper | Port B<br>Mode                    | Port    | Port C<br>Lower    |

| Always<br>1 for<br>I/O<br>Mode |              |                | 1 - I/P<br>o - O/P<br>o - O/P |                 | o-Modeo 1 - I/P<br>1-Mode1 0 -O/P |         | 1 - I/P<br>0 - O/P |

|                                | Group A      |                |                               |                 | G                                 | Froup B |                    |

- نحتاج للاتصال بأجهزة الـI/O إلى:

- \_ إمكانية الوصول إلى مختلف المسجلات المذكورة, data) ... status,...

- يعتمد الوصول على تخطيط الـO. (I/O mapping)

- الذي أخذ شكلين أساسيين هما:9-100

- « الدخل/الخرج وفق تخطيط الذاكرة Memory-mapped I/O »

- « الدخل/الخرج المستقل Isolated I/O »

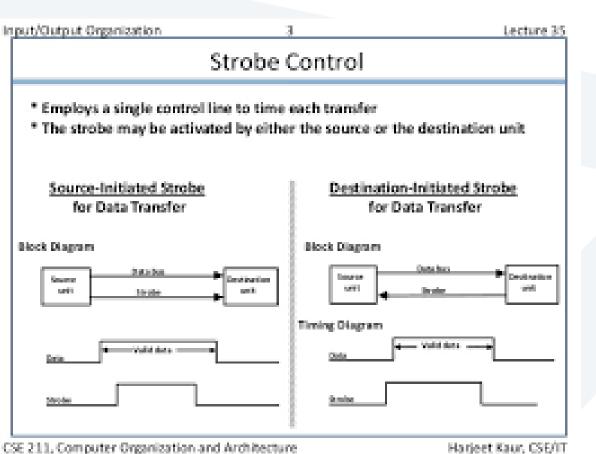

- \_ هنالك ثلاث أنماط من بروتوكولات الاتصال to send )

- data, ...)

- الدخل الخرج المبرمج Programmed I/O

- النفاذ المباشر إلى الذاكرة Direct memory access (DMA)

- الدخل الخرج المقاد بالمقاطعة Interrupt-driven I/O

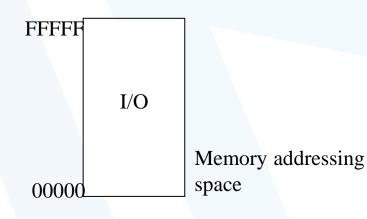

## I/O address mapping I/O تخطيط عنوان

Memory-mapped I/O وفقاً لتخطيط الذاكرة I/O –

- القراءة والكتابة شبيهة بالقراءة والكتابة من وفي الذاكرة.

- استخدام نفس إشارارت القراءة read والكتابة write.

- معظم المعالجات تستخدم هذا التخطيط أي I/O .mapping

- الدخل الخرج المستقل Isolated I/O:

- حيز عناوين I/O مستقل

- إشارات قراءة وكتابة مستقلة.

- تدعم معالجات Pentium الخرج المستقل .isolated I/O

- یخصص حیز عناوین مقداره 64 کیلوبایت 64 KB address space

- 8-, 16- يسمح بأية تشكيلة من تشكيلات » and 32-bit I/O ports

- \_ إضافة إلى دعمه الدخل الخرج وفقاً لتخطيط الذاكرة memory-mapped I/O.

#### البنيان Architecture

الوصول إلى أجهزة I/O

Accessing I/O DeviceS

Direct I/O

I/O

space

addressing

**Memory-mapped I/O**

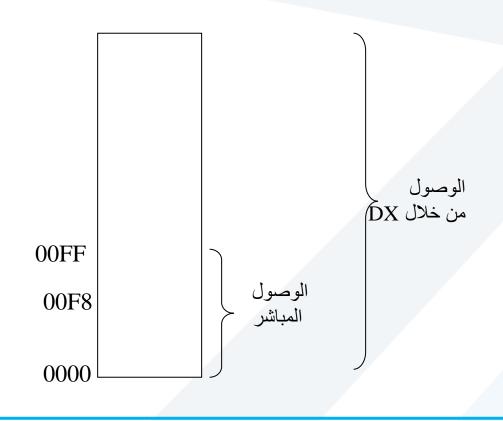

حيز عناوين البوابات في المعالج 8088 8088 Port Addressing Space

□حيز العنونة Addressing Space

□ الوصول المباشر من خلال التعليمات التالية:

IN AL, 80H IN AX, 6H 3CH, OUT ALOUT 0A0H, AX □ الوصول من خلال المسجل DX IN AL, DXIN AX, DXOUT DX, ALOUT DX, AX

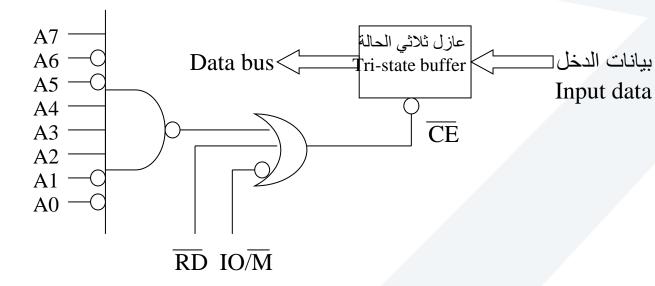

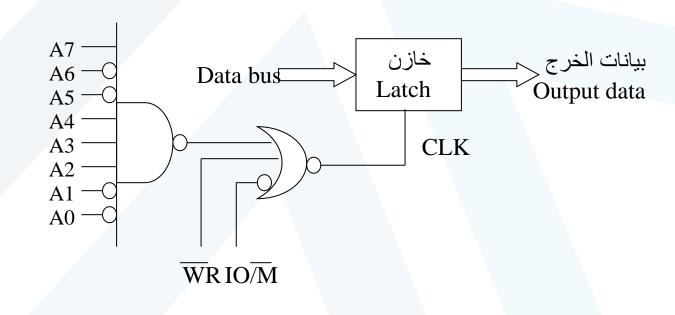

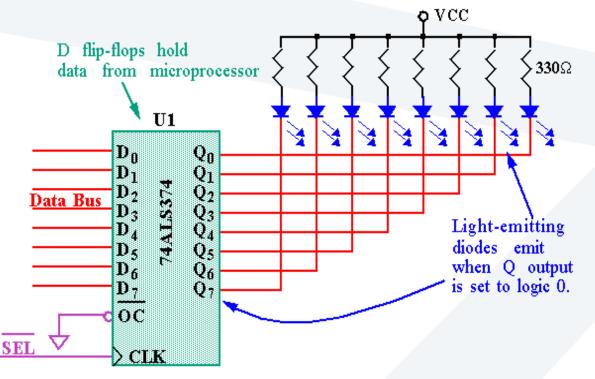

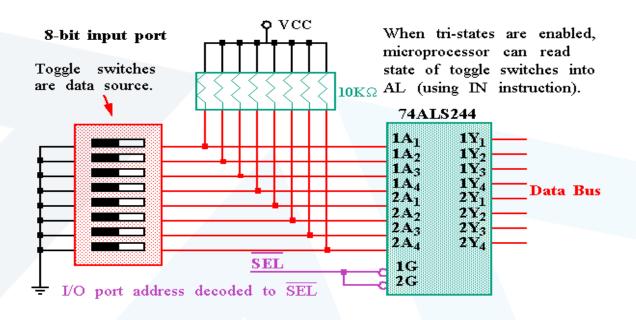

## تنفیذ بوابهٔ دخل Input Port Implementation

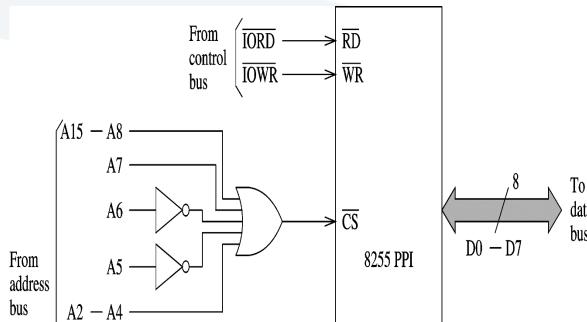

□ التنفيذ الداراتي Circuit Implementation بفرض أن عنوان بوابة الدخل هو 9CH

#### البنيان Architecture

— خرج الأجهزة المحيطية عالي الممانعة عند عدم اتصال المعالج مع بوابة الدخل.

—عند اتصال المعالج مع بوابة الخرج تنقل الأجهزة المحيطية بيانات الإدخال إلى باص بيانات الـCPU

— تتحكم دارة فك الترميز بمنح ممانعة الخرج قيمة عالية وبنقل بيانات الدخل إلى باص البيانات.

## طرق تبادل البيانات التفرعي

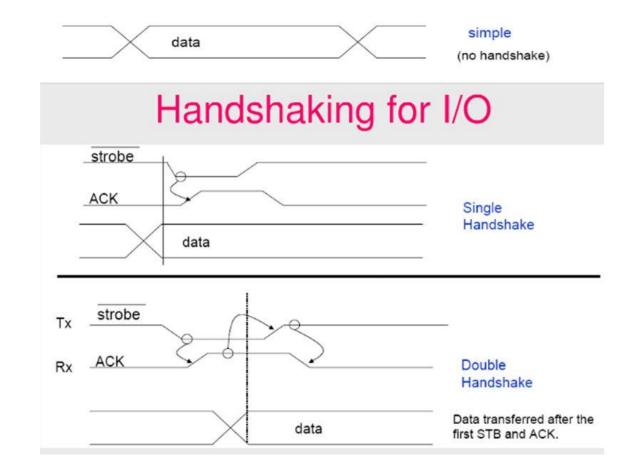

- 1. الإدخال الإخراج البسيطين Simple I/O.

- 2. الإدخال الإخراج النبضي البسيط Simple Strobed I/O.

- 3. استخدام المصافحة الأحادية Single Handshake I/O.

- . استخدام المصافحة الثنائية Double Handshake I/O

#### البنيان Architecture

أنواع الربط التفرعي

## مثال على أجهزة الـI/O Device I/O

## • لوحة المفاتيح Keyboard

- \_ يمسح متحكم لوحة المفاتيح ويحدد

- ضغطات المفاتيح وتركها. Key depressions and releases

- يزودنا بمعرف المفتاح كشيفرة مسح scan code

- \_ يمكننا النظر إلى شيفرة المسح كرقم تسلسلي يحدد المفتاح

- « تعتمد شيفرة مسح المفتاح على موقعه على لوحة المفاتيح

- « ليس له علاقة بقيمة ASCII الموافقة للمفتاح

- 8-bit parallel 8-BitK يحقق من خلال بوابة تفرعية سعة I/O port

- يمكن تحقيق ذلك من خلال الوحدة PPI 8255

## Architecture البنيان

تنفيذ بوابة خرج

## **Output Port Implementation**

□ النتفيذ الداراتي Circuit Implementation —بفرض عنوان بوابة الخرج هو 9CH.

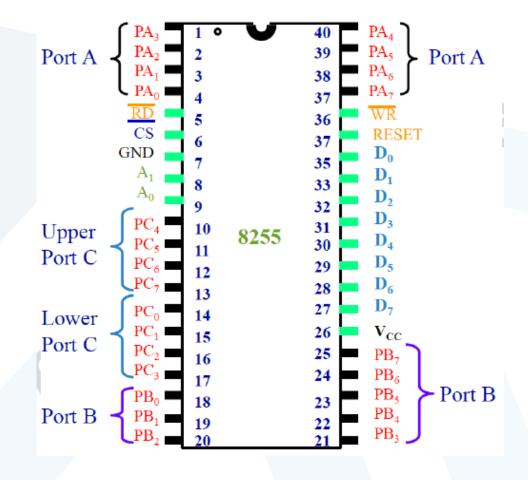

## وصل بوابات 8255 I/O ports

#### Architecture البنيان

I/O Device مثال على أجهزة الـ I/O Device

- Port A (PA)

- Port B (PB)

- Port C (PC)

\_ بفرض عناوين البوابة كما يلي

| 8255 register Po | ort | add | lress |

|------------------|-----|-----|-------|

|------------------|-----|-----|-------|

PA (input port) 60H

PB (output port) 61H

PC (input port) 62H

Command register 63H

## نقل بيانات الـI/O Data Transfer I/O

#### البنيان Architecture

- يتشابه تخطيط بوابات الدخل الخرج مع تخطيط الذاكرة:

- Partial mapping \_\_ تخطیط جزئي \_\_

- Full mapping \_\_ تخطيط كلي \_\_

- يمكننا قراءة حالة وشيفرة مسح لوحة المفاتيح عبر البوابة 60H

- هنالك شيفرة مسح من 7-bit

- PA0 PA6

- معرفة حالة المفتاح من خلال PA7

- PA7 = 0 key depressed

- PA0 = 1 key released

- تسير عملية نقل البيانات عبر طورين:

- \_ طور نقل البيانات

- ويمكن تحقيقه

- وحدات الدخل الخرج المبرمجة Programmed I/O

- DMA -

- \_ طور الإشعار من خلال:

- وحدات الدخل الخرج المبرمجة Programmed I/O

- المقاطعة Interrupt

- التقنيات الأساسية الثلاث Three basic techniques

- Programmed I/O -

- DMA -

- Interrupt-driven I/O –

## الوحدة المحيطية البينية القابلة للبرمجة 8255 8255 Programmable Peripheral Interface

#### البنيان Architecture

نقل بيانات الـI/O Data Transfer I/O

## Programmed I/O الدخل الخرج المبرمج

- ينفذ من خلال فترات الانتظار -busy waiting

- تسمى العملية بالاستفسار polling

- مثال Example

- \_ تتضمن قراءة مفتاح من لوحة المفاتيح:

- انتظار خانة PA7 لتأخذ القيمة low لتشير إلى أنه قد تم ضغط أحد المفاتيح لتشير إلى أنه قد تم ضغط أحد المفاتيح

- قراءة شيفرة المفتاح

- ترجمتها إلى قيمة الـ ASCII الموافقة

- الانتظار حتى ترك المفتاح.

## البنيا<u>ن Architecture</u>

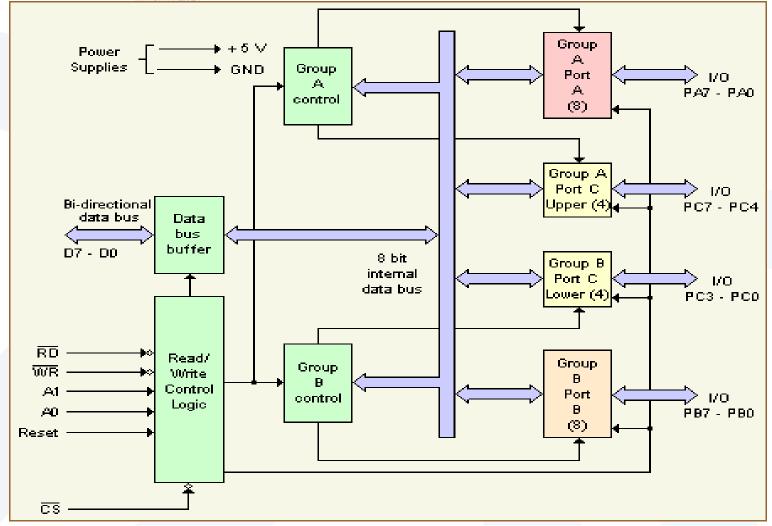

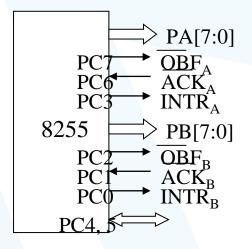

# المخطط الصندوقي

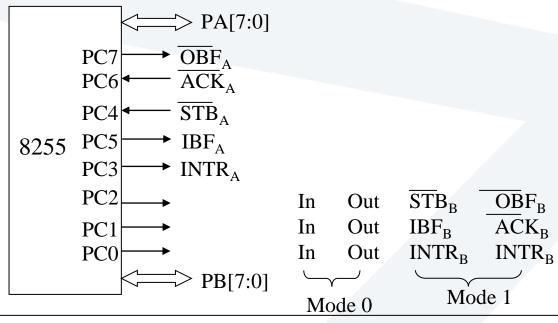

الوحدة المحيطية البينية القابلة للبرمجة 8255 Programmable Dariebarel Interfe

8255 Programmable Peripheral Interface

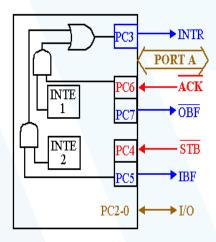

#### Group A

Port A (PA7-PA0) and upper half of port C (PC7 - PC4)

#### Group B

Port B (PB7-PB0) and lower half of port C (PC3 - PC0)

#### I/O Port Assignments

| $\mathbf{A_1}$ | $\mathbf{A_0}$ | Function         |

|----------------|----------------|------------------|

| 0              | 0              | Port A           |

| 0              | 1              | Port B           |

| 1              | 0              | Port C           |

| 1              | 1              | Command Register |

جَامعة

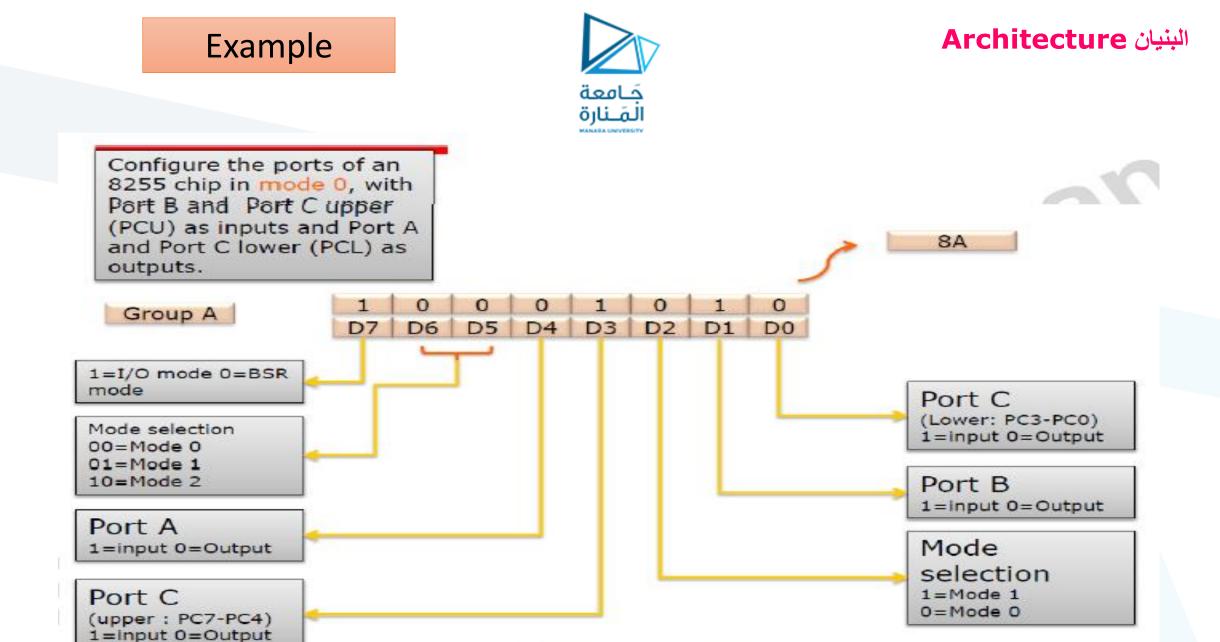

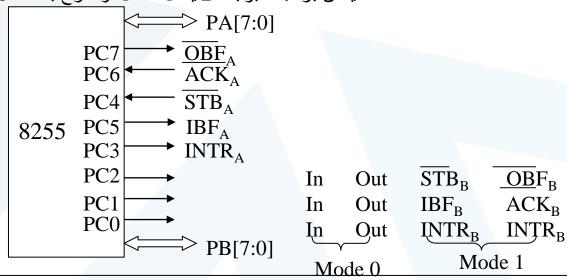

## برمجة الـProgramming 8255 8255

□ 8255 has three operation modes: *mode 0, mode 1, and mode 2*

https://manara.edu.sy/

## البنيان Architecture

ميزات أنماط العمل لـPPI 8255

النمط Mode 0 0! الدخل/الخرج البسيط **Simple Input or Output**

> تستخدم البوابتان ports A, B كبوابتين 8-bit I/O والبوابة C كبوابتن 4-bit.

يمكن برمجة أي من البوابات الأربع كدخل أو خرج بسيط ميزات الدخل/الخرج للبوابات الأربع في النمط 0 هي:

1-تخزين الخرج Outputs are latched

2-عدم تخزين الدخل Inputs are not latched

3-ليس هنالك إمكانية للمصافحة أو للمقاطعة.

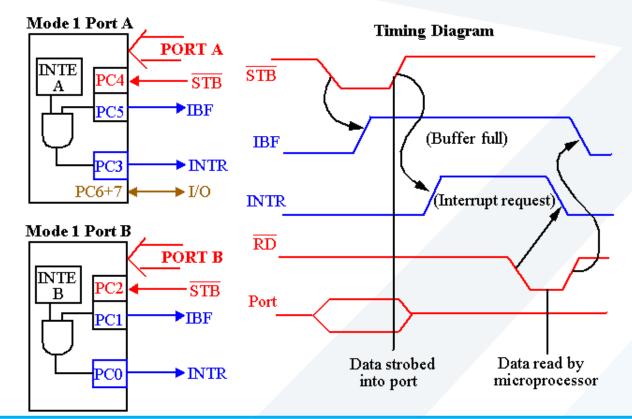

النمط Mode 1 1 إخراج مع مصافحة Mode 1 : **Output with Handshake**

يجري في هذا النمط تبادل إشارات المصافحة بين المعالج والوحد PPI 8255 قبل الشروع بنقل البيانات.

ميزات العمل بالنمط 1:

1-تعمل كلتا البوابتين A و B كبوابات دخل و (أو) خرج لـ8-bit مع مصافحة.

2-تستخدم كل من البوابتين A و B ثلاثة خطوط من البوابة ٢ كإشارات مصافحة ويمكن استخدام الخطين المتبقيين من C كخطوط إدخال/إخراج بسيط

3-تخزين الدخل والخرج.

4-دعم منطق المقاطعة

## ميز ات أنماط العمل لـ PPI 8255

النمط 2 Mode 2 نقل بيانات ثنائي الاتجاه Bidirectional Data : Transfer

يستخدم هذا النمط بشكل أساسي في تطبيقات نقل البيانات بين حاسوبين.

- 1. يمكننا تهيئة البوابة A في هذا النمط كبوابة ثنائية الاتجاه، بينما تعمل البوابة B في أحد النمطين 0 أو 1.

- 2. تستخدم البوابة A خمس من خطوط البوابة C لإشارات المصافحة عند تبادل البيانات.

- 3. يمكننا استخدام الخطوط الثلاث المتبقية من البوابة C كخطوط دخل/خرج بسيط أو كإشارات مصافحة للبوابة B.

The strobe input loads data into the port latch on a 0-to-1 transition

IFB Input buffer full is an output indicating that the input latch contain information

INTR Interrupt request is an output that requests an interrupt

INTE The interrupt enable signal is neither an input nor an output; it is an internal bit programmed via the PC4(port A) or PC2(port B) bits.

PC7,PC6 The port C pins 7 and 6 are general-purpose I/O pins that are available for any purpose.

#### البنيان Architecture

## برمجة الـProgramming 8255 8255

#### □ النمط Mode 0 0:

سيمكننا برمجة البوابات A, B, و C بشكل إفرادي كبوابات دخل أوخر C سيمكن تقسيم البوابة C إلى بوابتين مستقلتين عن بعضهما كل منهما C

#### :1 Mode 1

— تبرمج البوابتان A و B كبوابات دخل أو خرج — تستخدم البوابة C لأجل المصافحة handshaking.

### البنيان Architecture

## ميزات أنماط العمل لـ8255 PPI

: Mode 2 ، 2 النمط 1

```

ـــتبرمج البوابة A لتكون ثنائية الاتجاه

```

handshaking للمصافحة C البوابة

\_\_يمكن برمجة البوابة Bليعمل كدخل أو خرج بانمط 0 أو بالنمط 1.

- . صمم مفكك ترميز لتفعيل شريحة 8255 عند العنوان 40H؟

- 2. اكتب مجموعة التعليمات التي تسمح بتشغيل البوابة A في وحدة 8255 بالنمط 0 دخل و-PC4 PC0 و PC0-PC3 كدخل و-PC4 كدخل و-PC4

PC7 كخرج؟

## ميزات أنماط العمل لـ8255 PPI

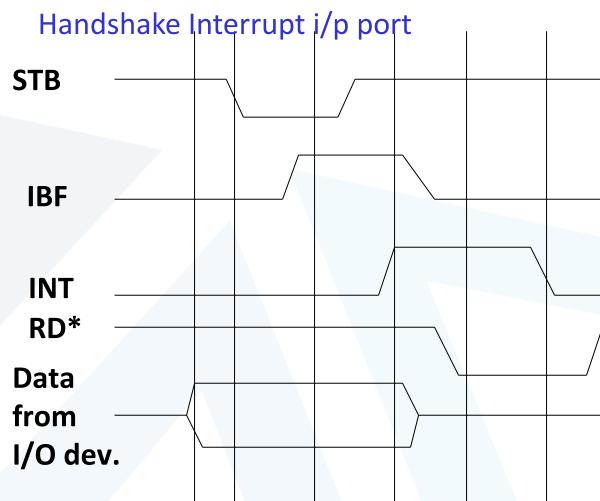

يمكن رسم المخطط الزمني من مزيج من مخططي Mode 1 Strobed يمكن رسم المخطط الزمني من مزيج من مخططي Input.

| DIED | <b></b>                                                                                             |                 |

|------|-----------------------------------------------------------------------------------------------------|-----------------|

| INTR | Interrupt request is an output that requests an interrupt                                           | كامعة           |

| OBF  | Output buffer full is an output indicating that the output contains data for the bi-directional bus | المَـــibuffeti |

Acknowledge is an input that enables tri-state buffers which are otherwise in their high-impedance state

STB The strobe input loads data into the port A latch

IFB Input buffer full is an output indicating that the input latch contains information for the external bi-directional bus

INTE Interrupt enable are internal bits that enable the INTR pin.

Bit PC6(INTE1) and PC4(INTE2)

PC2,PC1 Theses port C pins are general-purpose I/O pins that are and PC0 available for any purpose.

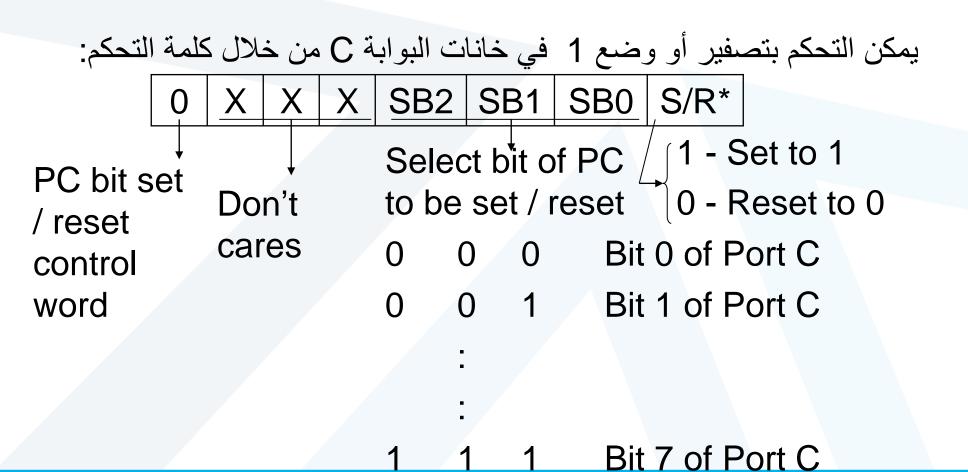

# كلمة التحكم بتصفير وتحميل خانات البوابة C PCBSR Control word contd.

يمكن التحكم بتصفير أو وضع 1 في خانات البوابة C من خلال كلمة التحكم: SB2 | SB1 | S/R\* SB0 X 1 - Set to 1 Select bit of PC PC bit set to be set / reset 0 - Reset to 0 Don't / reset cares Bit 0 of Port C 0 control 0 Bit 1 of Port C word Bit 7 of Port C

كلمة التحكم بتصفير وتحميل خانات البوابة C PCBSR Control word ontd.

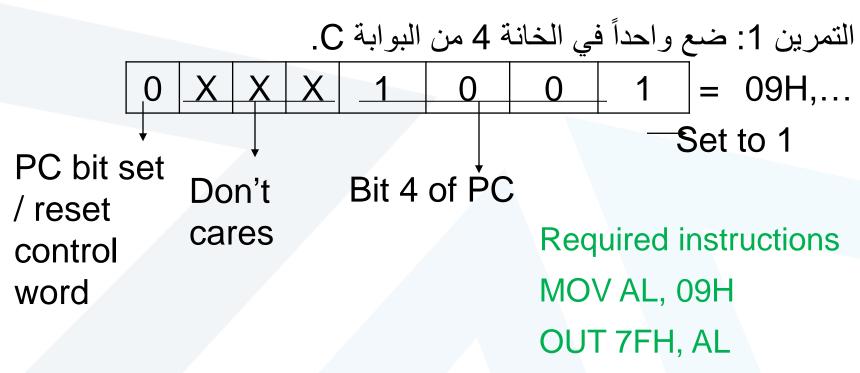

التمرين 1: ضع واحداً في الخانة 4 من البوابة C.

$0 \mid X \mid X \mid X \mid 1 \quad 0 \quad 0 \quad 1 \quad = \ 09H,...$

Set to 1

PC bit set

/ reset

control

word

Don't Bit 4 of PC cares

Required instructions MOV AL, 09H OUT 7FH, AL

#### البنيان Architecture

كلمة التحكم بتصفير وتحميل خانات البوابة C PCBSR Control word contd.

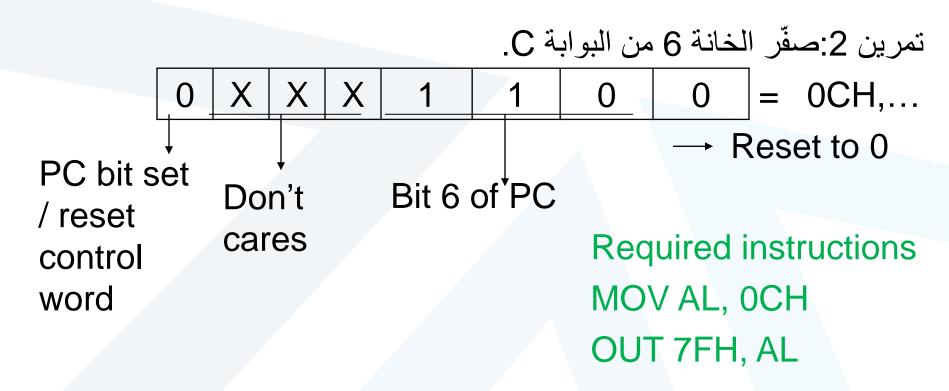

تمرين 2: صفر الخانة 6 من البوابة C.

$0 \mid X \mid X \mid X \mid 1 \quad 1 \quad 0 \quad 0 = 0CH,...$

Reset to 0

PC bit set

/ reset

control

word

Don't cares

Bit 6 of PC

Required instructions MOV AL, 0CH OUT 7FH, AL

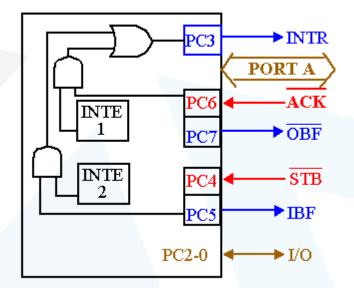

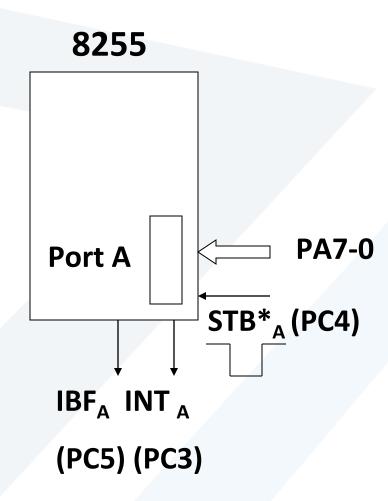

# البنيان Architecture البنيان A مصافحة المقاطعة لبوابة الدخل

## Handshake Interrupt I/o port

نهايات المصافحة العاملة مع البوابة A عند عملها كدخل:

INT<sub>A</sub> is PC3

STB\*<sub>A</sub> is PC4

IBF<sub>A</sub> is PC5

المصافحة والمقاطعة لبوابة الدخل

عندما يكون لدى جهاز الخرج بيانات يرغب بإرسالها إلى المعالج عبر البوابة B العاملة بالنمط 1 دخل فإن الجهاز يختبر فيما إذا كانت الإشارة القادمة من النهاية (input buffer full)=0

فإذا كانت =0، يقوم بإرسال البيانات عبر النهايات PB7-0 ويفعل إشارة (Strobe) \*STB الفعالة عند المستوي المنخفض.

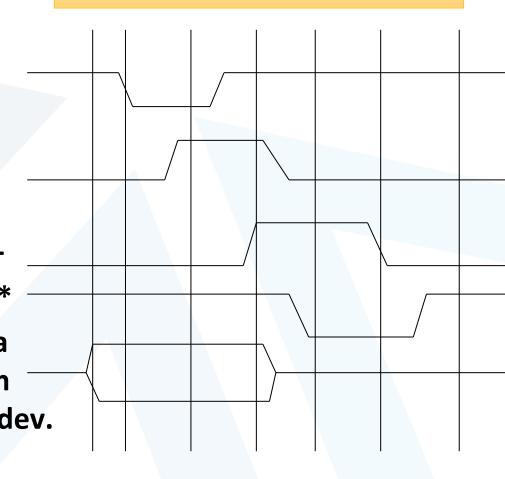

عندما تنتقل إشارة \*STB إلى المستوي المرتفع، تدخل البيانات البوابة ويجري تفعيل النهاية IBF.

في حال تمكين المقاطعة تفعل إشارة INT مما يؤدي إلى مقاطعة المعالج.

يقوم المعالج بقراءة البوابة أثناء فعالية إشارة المقاطعة ومن ثم يلغي تفعيل الإشارتين IBF و INT.

| الكلمة<br>المختزلة | المعنى                   | الصيغة              | العملية                                                                                                                                                          | الأعلام<br>المتأثرة |

|--------------------|--------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| CALL               | مناداة<br>برنامج<br>فرعي | CALL<br>operan<br>d | يتابع التنفيذ في البرنامج الفرعي<br>من العنوان المحدد بالمتحول<br>operand و المعلومات<br>المطلوبة من أجل العودة مثلIP<br>و cs يتم حفظها أوتوماتيكيا في<br>المكدس | لا يوجد             |

| ۱<br>۱ |                        |

|--------|------------------------|

| 1      | جَـامعة<br>الـمَــنارة |

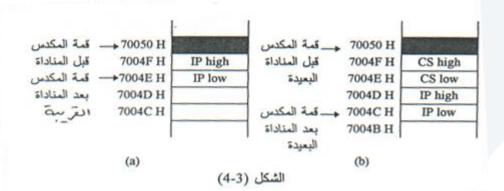

## تعليمات استدعاء البرامج الفرعية

البرامج الفرعية هي إجراءات مكتوبة بشكل مستقل عن البرنامج الرئيسي . متى وجب على البرنامج الرئيسي أن ينجز الوظيفة المحددة بواسطة البرنامج الفرعى الى العمل و من أجل هذا يجب أن يتحول التحكم من البرنامج الرئيسي الى نقطة البداية للبرنامج الفرعي حيث يستمر تنفيذ البرنامج الفرعي و عند اكتمال تنفيذه يعود التحكم الى البرنامج الرئيسي بالتعليمة التالية لتعليمة مناداة البرنامج الفرعي

#### تعليمة المناداة

. بعد حفظ عنوان العودة فان القيمة الجديدة ذات 16 بت و التي تقابل حجرة تخزين أمثلة على متحولات . ١٦ التعليمة الأولى من البرنامج الفرعى يتم تحميلها في المناداة القربية:

CALL near - proc CALL [SI] **CALL BX**

#### • تعليمة العودة:

إن كل برنامج فرعى يجب أن ينتهى بتنفيذ التعليمة التي تعيد التحكم إلى البرنامج الرئيسي و هي تعليمة العودة , RET

#### **Operand** المناداة ضمن نفس Near- proc Memptr 16 Regptr 16 Far - proc Memptr 32

مقطع الشيفرة

المناداة من مقطع شيفر ة آخر

البرنامج الرئيسي هو كالتالي:

MAIN PROGRAM

MAIN PROG SEGMENT

**ASSUME CS: MAIN PROG**

MOV AX, 5000 H

MOV DS,AX

MOVAX,6000 H

MOV SS, AX

MOV SP, 0100 H

MOV BX, 2000 H

MOV AL,[SI]

MOV CX,[DI]

**CALL MULT**

MOV [BX], AX

MOV [ BX+2 ], DX

HLT

MAIN PROG ENDS

أما البرنامج الفرعي فهو كالتالي:

SUBROUTINE SUPR SEGMENT

ASSUME CS: SUBR

MULT PROC FAR

**CBW**

IMUL CX

**RET**

MUL T ENDP

**SUBR ENDS**

#### البنيان Architecture

ملاحظة إذا وجد المتحول operand فهو إزاحة ذات bit 16.

| الكلمة   | المعنى   | الصيغة   | العملية                     | الأعلام  |

|----------|----------|----------|-----------------------------|----------|

| المختزلة |          |          |                             | المتأثرة |

|          |          | RET/ RET | يتابع التنفيذ في البرنامج   | لا يوجد  |

| RET      | عودة إلى | operand  | الرئيسي بعد استرجاع قيمة IP |          |

|          | البرنامج |          | و قيمة CS من أجل المناداة   |          |

|          | الرئيسي  |          | البعيدة) إذا وجد المتحول    |          |

|          |          |          | operand في تعليمة العودة    |          |

|          |          |          | فانه يضاف إلى محتويات       |          |

|          |          |          | spll                        |          |

#### ثال

اكتب برنامجا فرعيا يستدعى من قبل برنامج رئيسي في مقطع شيفرة آخر. البرنامج الفرعي يضرب عدداً ذا إشارة بطول بايتين مع عدد ذي إشارة بطول بايت واحد و مخزن CX مخزن في البرنامج الرئيسي يستدعي البرنامج الفرعي ثم يخزن . ALفي البرنامج الرئيسي يستدعي البرنامج الذاكرة المشار إليها بواسطة يشير DIيشير إلى العدد الذي طوله بايت واحد و SIافترض أن العدد الأخر .

## تنفیذ بوابهٔ خرج Output Port Implementation

## Architecture البنيان

تنفيذ بوابة دخل

## **Input Port Implementation**

## وصل بوابات 8255 I/O ports

A0

## Architecture البنيان

## I/O Device مثال على أجهزة ال- I/O Device

• تمتلك الوحدة PPI 8255 ثلاث مسجلات بعرض -8 bit

A0

- Port A (PA)

- Port B (PB)

- Port C (PC)

\_ بفرض عناوين البوابة كما يلى

| 8255 register    | Port address |

|------------------|--------------|

| PA (input port)  | 60H          |

| PB (output port) | 61H          |

| PC (input port)  | 62H          |

| Command register | 63H          |

## نقل بيانات الـI/O Data Transfer I/O

- المَارة تسير عملية نقل البيانات عبر طورين:

- طور نقل البيانات

- ويمكن تحقيقه

- وحدات الدخل الخرج المبرمجة Programmed I/O

- DMA -

- \_ طور الإشعار من خلال:

- وحدات الدخل الخرج المبرمجة Programmed I/O

- المقاطعة Interrupt

- Three basic techniques التقنيات الأساسية الثلاث

- Programmed I/O

- DMA -

- Interrupt-driven I/O -

#### Architecture البنيان

يتشابه تخطيط بوابات الدخل الخرج مع تخطيط الذاكرة:

- تخطیط جزئي Partial mapping

- تخطیط کلی Full mapping

- يمكننا قراءة حالة وشيفرة مسح لوحة المفاتيح عبر البوابة 60H

- هنالك شيفرة مسح من 7-bit

- PA0 PA6

- معرفة حالة المفتاح من خلال PA7

- PA7 = 0 key depressed

- PA0 = 1 key released

## برمجة الـProgramming 8255 8255

جًامعة المَـنارة

ـــتبرمج البوابة A لتكون ثنائية الاتجاه ـــتستخدم البوابة C للمصافحة handshaking ـــستخدم البوابة Bليعمل كدخل أو خرج بانمط 0 أو بالنمط 1.

- 1. صمم مفكك ترميز لتفعيل شريحة 8255 عند العنوان 40H؟

- mode كنب مجموعة التعليمات التي تسمح بتشغيل البوابة A في وحدة 8255 بالنمط 0 دخل 0, port A as input 0, port A as input 0 خرج 0 کدخل 0 کخرج؟

#### البنيان Architecture

## نقل بيانات الـI/O Data Transfer I/O

- الدخل الخرج المبرمج Programmed I/O

- busy-waiting ينفذ من خلال فترات الانتظار

- تسمى العملية بالاستفسار polling

- مثال Example

- \_ تتضمن قراءة مفتاح من لوحة المفاتيح:

- انتظار خانة PA7 لتأخذ القيمة low

- لتشير إلى أنه قد تم ضغط أحد المفاتيح

- قراءة شيفرة المفتاح

- ترجمتها إلى قيمة الـ ASCII الموافقة

- الانتظار حتى ترك المفتاح.

INTR Interrupt request is an output that requests an interrupt

Output buffer full is an output indicating that the output buffer contains data for the bi-directional bus

Acknowledge is an input that enables tri-state buffers which are otherwise in their high-impedance state

STB The strobe input loads data into the port A latch

IFB Input buffer full is an output indicating that the input latch contains information for the external bi-directional bus

INTE Interrupt enable are internal bits that enable the INTR pin.

Bit PC6(INTE1) and PC4(INTE2)

PC2,PC1 Theses port C pins are general-purpose I/O pins that are and PC0 available for any purpose.

يمكن رسم المخطط الزمني من مزيج من مخططي Mode 1 Strobed Input و Mode 1 Strobed Output.

#### البنيان Architecture

كلمة التحكم بتصفير وتحميل خانات البوابة C 8255 PCBSR Control word contd.

### البنيان Architecture

مصافحة المقاطعة لبوابة الدخل A Handshake Interrupt i/p port

نهايات المصافحة العاملة مع البوابة Δ عند عملها كدخل:

$INT_{A}$  is PC3

STB\*<sub>A</sub> is PC4

$IBF_{A}$  is PC5

## المصافحة والمقاطعة لبوابة الدخل Handshake Interrupt i/p port

## Architecture البنيان

المصافحة والمقاطعة لبوابة الدخل Handshake Interrupt i/p port

INT عندما تنتقل إشارة \*STB إلى المستوي المرتفع، تدخل البيانات البوابة \*RD ويجري تفعيل النهاية IBF.

في حال تمكين المقاطعة تفعل إشارة INT مما يؤدي إلى مقاطعة المعالج.

يقوم المعالج بقراءة البوابة أثناء فعالية إشارة المقاطعة ومن ثم يلغي تفعيل الإشارتين IBF و INT.

# البنيان Architecture

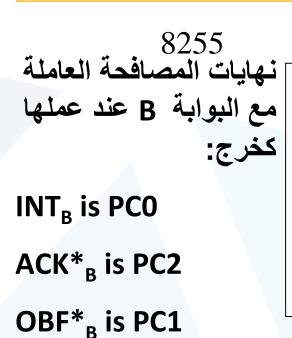

المصافحة والمقاطعة لبوابة الخرج B Handshake Interrupt i/p port

## اختبار حالة المصافحة في عمليات ١/٥

يمكن إلغاء تفعيل المقاطعة من خلال كلمة تفعيل وتصفير البوابة PCBSR) C

حتى لو وردت بيانات جديدة إلى عازل بوابة الدخل من جهاز خارجي من خلال المقاطعة، فلن تفعل مقاطعة بوابة الخرج.

كذلك الأمر حتى لو أفرغ جهاز الـ10 عازل الخرج بعملية مقاطعة الخرج، فلن تفعل مقاطعة الدخل.

لذلك يقوم المعالج بقراءة حالة البوابة.

## Architecture البنيان

المصافحة والمقاطعة لبوابة الخرج B Handshake Interrupt i/p port

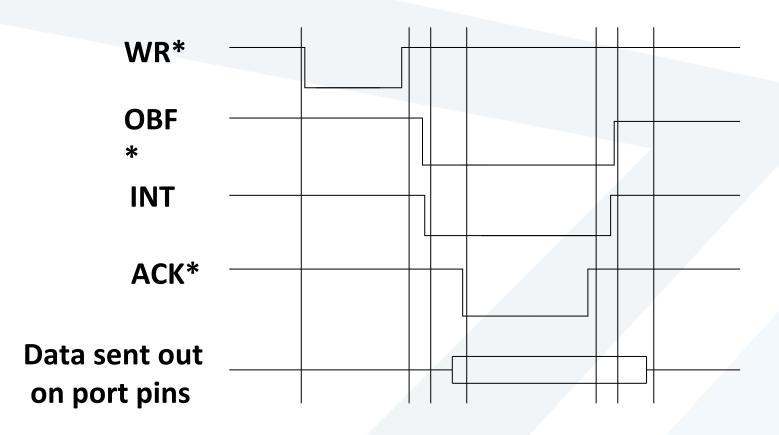

عندما يرغب جهاز الخرج باستقبال بيانات عبر إحدى البوابات فإنه يختبر فيما إذا كانت لإشارة 0= (output buffer full)

ويفعل إشارة PB7-0، يقوم باستقبال البيانات عبر النهايات PB7-0 ويفعل إشارة ACK. (Acknowledge)  $\overline{ACK}$

عندما تنتقل إشارة  $\overline{ACK}$  إلى المستوي المرتفع، يجري إخراج البيانات من البوابة تأخذ $\overline{ACK}$ قيمة الـ1.

وإذا جرى تمكين مقاطعة البوابة يجري تفعيل النهاية INT. مما يؤدي إلى مقاطعة عمل لمعالج.

بقوم المعالج بإرسال بايت أخرى إلى البوابة أثناء فعالية إشارة المقاطعة مما يؤدي إلى نصفير كل من الإشارتين ACKو INT.

عند عدم العمل بالنمط صفر يمكن استخدام C كدلالة على حالة PA & PB

| P | <b>C7</b> | PC6 F | PC5 | PC4 F | PC3 F | PC2  | PC1      | PC0 |

|---|-----------|-------|-----|-------|-------|------|----------|-----|

|   | OBF*      | INTE  | IBF | INTE  | INT   | INTE | IBF/OBF* | INT |

|   | _         | •     |     |       |       |      |          |     |

PA status in Mode 1 o/p (along with INT)

PA status in Mode 1 i/p

PB status in Mode 1

i/p or o/p

PA status in Mode 2

IBF = i/p buffer full

**INT** = **Interrupt**

OBF\* = o/p buffer full

**INTE** = Interrupt Enable