جامعة المنارة كلية الهندسة هندسة معلوماتية

# الدارات الرقمية Digital Circuits CECC323

مدرسة المقرر د. بشرى علي معلا

# تابع للدارات التتابعية

✓ العدادات✓ المسجلات

✓ العداد: دارة منطقية تتابعية لديها القدرة على العد ثنائياً بترتيب معين : تصاعدياً (Up Counting)، تنازلياً (Down)

ر (Counting) ، أو بأي ترتيب آخر

✓ أثناء عملية العد تدعى كل قيمة يصل إليها العداد حالة (State)

كينتقل العداد من حالة إلى أخرى مع نبضات التزامن (clock) و بترتيب معين

بمكن للعداد أن يبدأ العد من أية حالة من حالاته و تسمى هذه الحالة بالحالة الابتدائية (initial state)

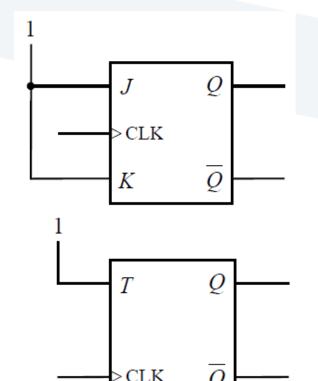

حتبنى العدادات باستخدام باستخدام القلاب JK أو القلاب T

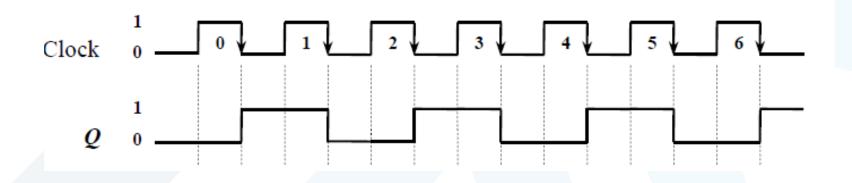

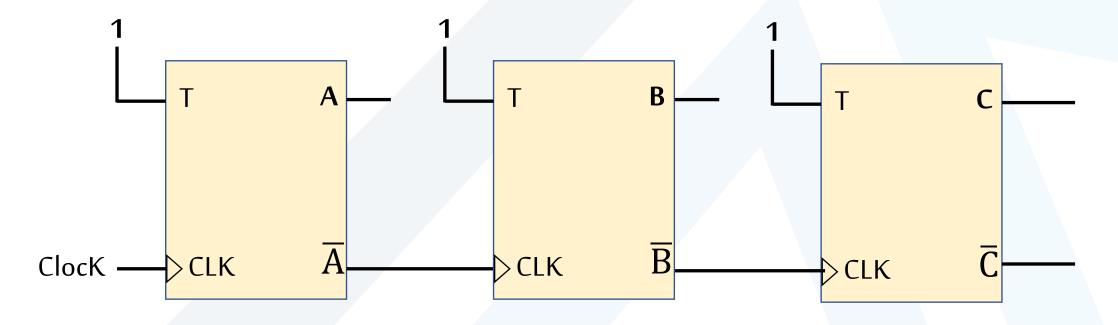

﴿ في هذا الوضع يعكس القلاب حالته مع كل نبضة من نبضات التزامن كما في الشكل:

نلاحظ أن إشارة خرج القلاب يمكن أيضاً اعتبارها إشارة تزامن لكن ترددها نصف تردد إشارة التزامن الداخلة إليه  $f_C$  و كأن القلاب قد قام بتقسيم التردد على 2:  $f_Q = \frac{1}{2} f_C$

## العد تصاعدياً (Up Counting)

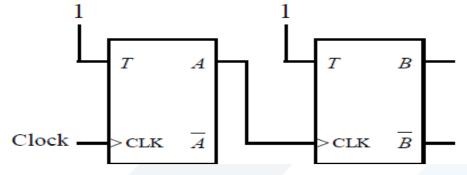

﴿إذا أدخلنا إشارة خرج القلاب الأول كإشارة تزامن إلى قلاب ثاني من النوع ذاته هذا سيجعل القلاب الثاني يقسم تردد تلك الإشارة على 2

﴿ فيكون مخطط التزامن:

$$f_B = \frac{1}{2} f_A = \frac{1}{4} f_{Clk}$$

| ﴿ بملاحظة الإشارة يظهر لدينا أن A تغير حالتها كل نبضة تزامن أي بمكن اعتبارها الخانة LSB بينما B تغير |

|------------------------------------------------------------------------------------------------------|

| حالتها كل نبضتي تزامن فهي يمكن اعتبارها خانة ثانية .                                                 |

﴿ يمكن اعتبار أن ما لدينا هو عداد تصاعدي ذي خانتين يمكن من مخطط التزامن تحديد التسلسل:

| Clock |     | 0 | 1 | 2 | 3   | 4 | 5 | 6 |

|-------|-----|---|---|---|-----|---|---|---|

| A     | 1 0 | 0 | 1 | 0 | 1 👢 | 0 | 1 | 0 |

| В     | 0   | 0 | 0 | 1 | 1   | 0 | 0 | 1 |

| В | А | State | ير |

|---|---|-------|----|

| 0 | 0 | 0     |    |

| 0 | 1 | 1     |    |

| 1 | 0 | 2     |    |

| 1 | 1 | 3     |    |

| 0 | 0 | 0     |    |

| 0 | 1 | 1     |    |

| 1 | 0 | 2     |    |

بناء العدادت

## العد تصاعدياً (Up Counting)

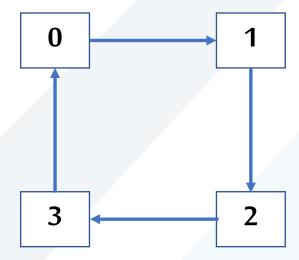

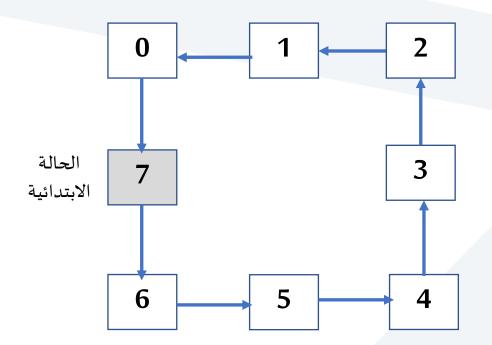

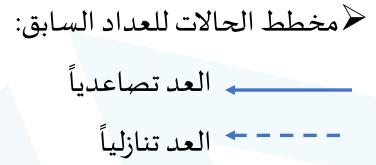

مخطط الحالات:

العدو مخطط الحالات و ذلك إذا بدأ العداد العد من الحالة 3 bits up counting

- $\sqrt{}$  نحتاج عدد قلابات = عدد خانات العداد=3

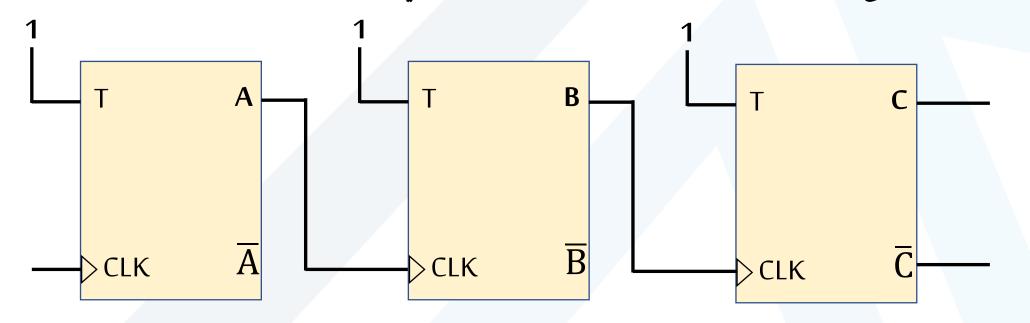

- ✓ ندخل الخرج غير المعكوس لكل قلاب كإشارة تزامن للقلاب التالي له

C B A

$3 = (0 \ 1 \ 1)_2$

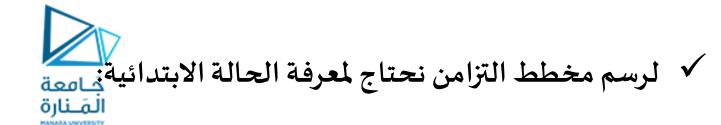

✓ لرسم مخطط التزامن نحتاج لمعرفة الحالة الابتدائية:

| В | А | State | امعة<br>مــنارة |

|---|---|-------|-----------------|

| 1 | 1 | 3     | MANARA UNIVE    |

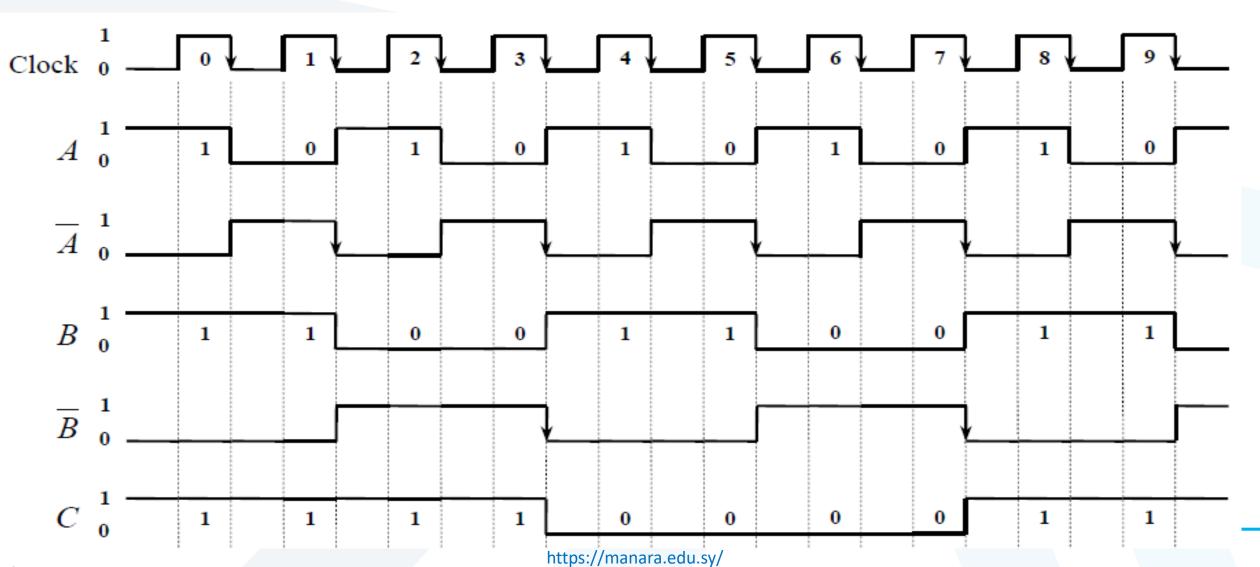

✓ الجدول المجاور يوضح تسلسل العد:

√ مخطط الحالات لم يتغير رغم أن الحالة الابتدائية كانت3

| С | В | А | State    |

|---|---|---|----------|

| 0 | 1 | 1 | 3        |

| 1 | 0 | 0 | 4        |

| 1 | 0 | 1 | 5        |

| 1 | 1 | 0 | 6        |

| 1 | 1 | 1 | 7        |

| 0 | 0 | 0 | 0        |

| 0 | 0 | 1 | 1        |

| 0 | 1 | 0 | 2        |

| 0 | 1 | 1 | 3        |

| 1 | 0 | 0 | 4        |

| • | • | * | <b>:</b> |

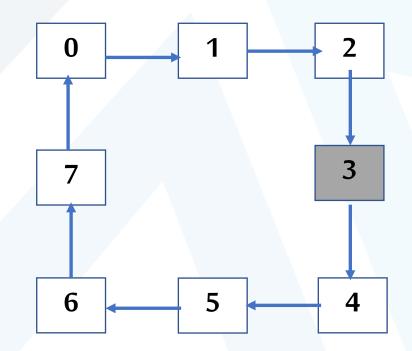

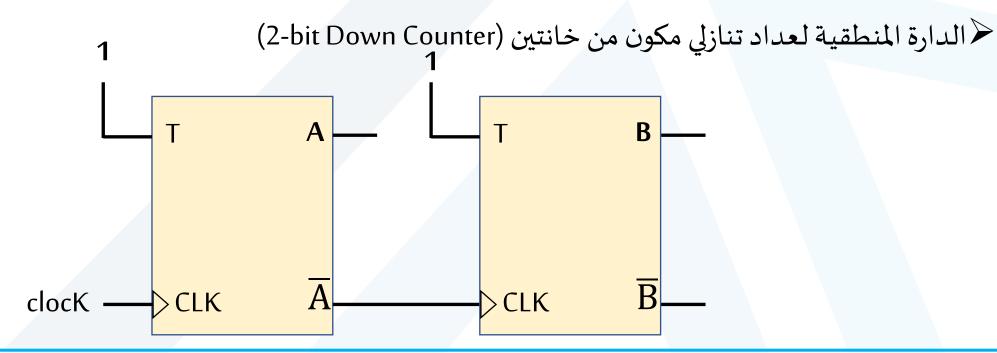

## ( Down Counting) العد تنازلياً

﴿إذا أدخلنا إشارة الخرج المعكوس للقلاب الأول كإشارة تزامن إلى قلاب ثاني من النوع ذاته فهذا سيجعل العداد يقوم بالعد تنازلياً

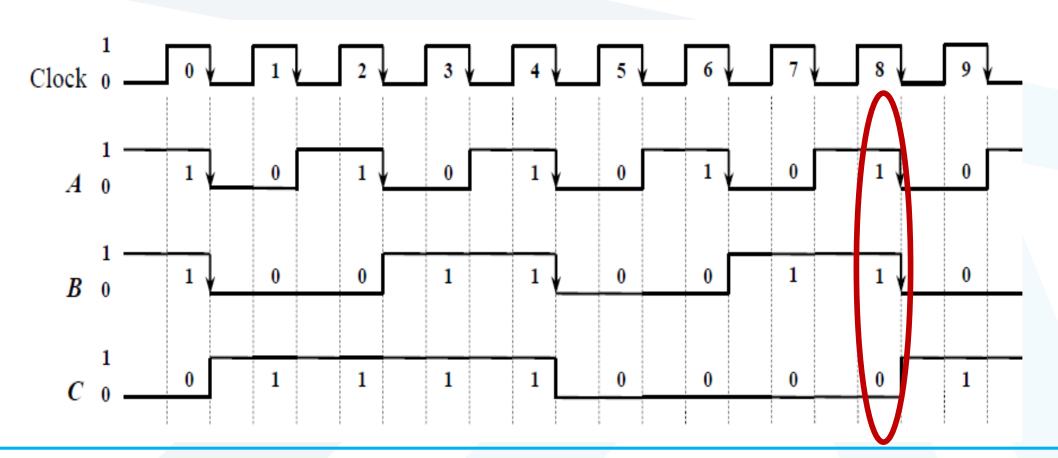

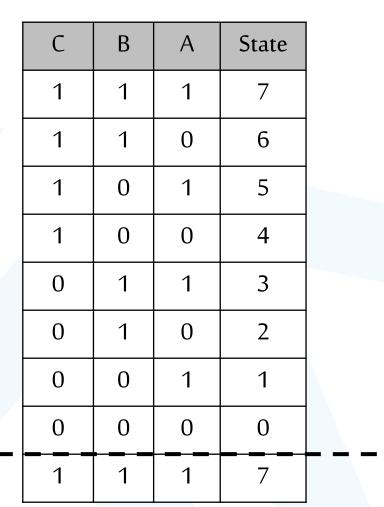

مثال1: صمم عداداً تنازلياً ذي ثلاث خانات (3- bit down counting)وارسم مخطط التزامن له، ثم وضح تسلسل

العد و مخطط الحالات و ذلك إذا بدأ العداد العد من الحالة 7

الدارة المنطقية لعداد تنازلي مكون من ثلاث خانات (3-bit Down Counter)

C B A  $7 = (1 1 1)_2$

## ✓ الجدول المجاور يوضح تسلسل العد:

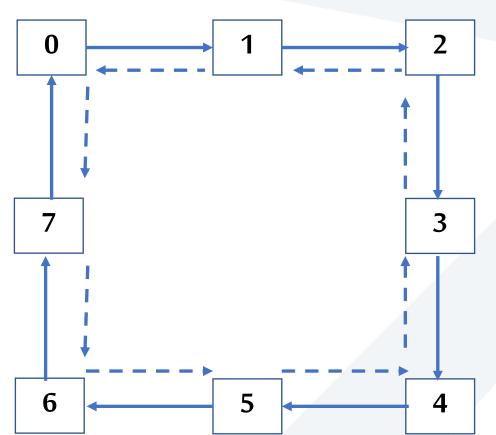

## ✓ مخطط الحالات:

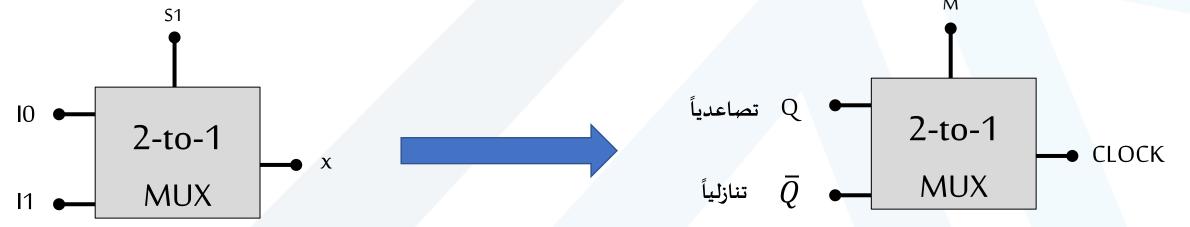

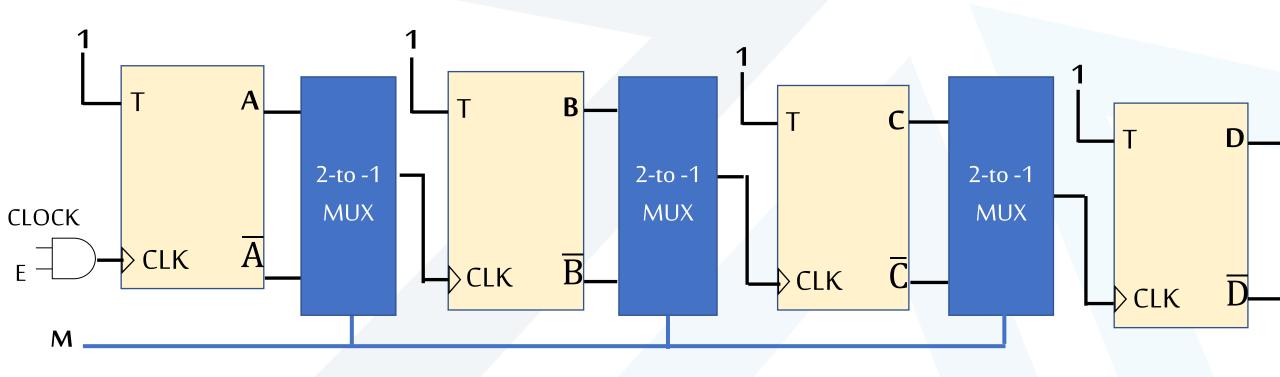

#### ( Up/ Down Counting ) العد بالاتجاهين

| M | CLOCK   |

|---|---------|

| 0 | Q       |

| 1 | $ar{Q}$ |

﴿ هو عداد يقوم بالعد تصاعدياً و تنازلياً حسب قيمة إشارة التحكم

- يقوم بالعد تصاعدياً من أجل M=0

- يقوم بالعد تنازلياً من أجل M=1

◄ بما أن ربط القلابات مع بعضها يختلف بحسب اختلاف نوع العد لذا نحتاج إلى استخدام ناخب 2to1 Mux لتحقيق ذلك

حيث يُدخل الخرج المعكوس والخرج غير المعكوس للقلاب إلى دخلي الناخب الذي يحدد أيهما يُمرر كإشارة تزامن حسب قيمة إشارة التحكم M .

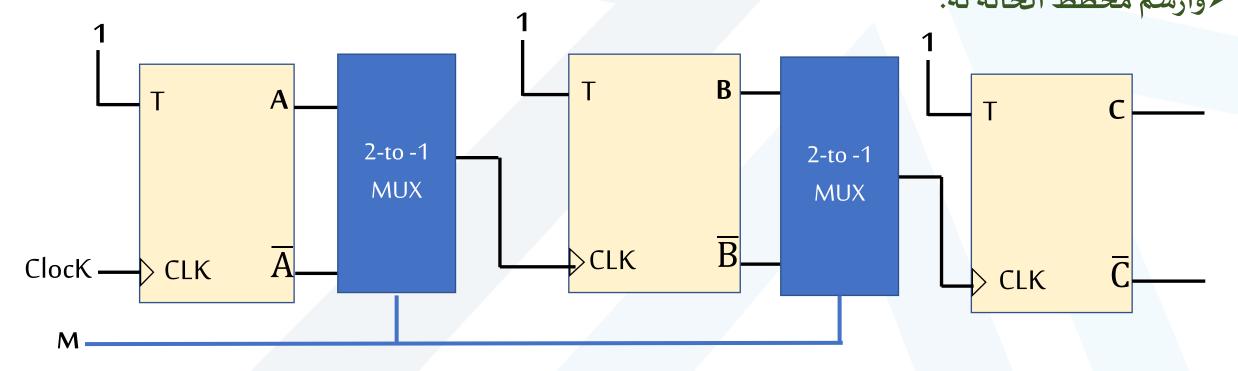

## (Up/Down Counting) العد بالاتجاهين

﴿ مثال: صمم عداد ذي ثلاث خانات (3 bit counter) يقوم بالعد تصاعدياً و تنازلياً إذا بدأ العداد العد من الحالة ٠ وارسم مخطط الحالة له.

## ( Up/ Down Counting) العد بالاتجاهين

- مثال: صمم عداد ذي أربعة خانات (4bit counter) يستجيب لإشارتي تحكم E,M بحيث:

- الإشارة M تحدد ترتيب العد للعداد :

- فيقوم بالعد تصاعدياً عندما تكون مساوية من 0

- تنازلیاً عندما تکون مساویة 1

- ✓ والإشارة E عبارة عن إشارة سماح (ENABLE) تسمح للعداد بالعمل عندما تكون مساوية 1 توقف العداد عن العد عن العد عندما تكون مساوية 0

عندما تكون مساوية 0

- E \_\_\_\_\_

- ◄ عدد الخانات =عدد القلابات =4

- ✓ عداد تصاعدي /عداد تنازلي: نحتاج إلى ناخب 2to1 لتحديد نوع العد يتحكم بذلك الإشارة М

- ✓ عداد في حالة عمل /حالة توقف

بما أن العداد يستمر في العد طالما إشارة التزامن CLOCK مستمرة فهذا يعني أننا بحاجة في حالة إيقاف العداد إلى إلغاء تأثير إشارة التزامن . هذا يكون من خلال إدخال هذه الإشارة مع إشارة السماح E على بوابة AND

## الدارة المنطقية للعداد:

المسجلات (Registers)

### المسجلات (registers)

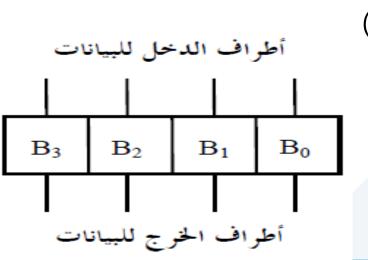

المسجل: موقع تخزيني له القدرة على اختزان معلومة مكونة من عدة خانات.

◄ المسجل: أنه جزء مهم من أي معالج CPU

المعالج المكون من عدة مسجلات يخفض عدد مرات الولوج إلى الذاكرة وبالنتيجة يبسط تنفيذ المهام البرمجية ويخفض زمن تنفيذها.

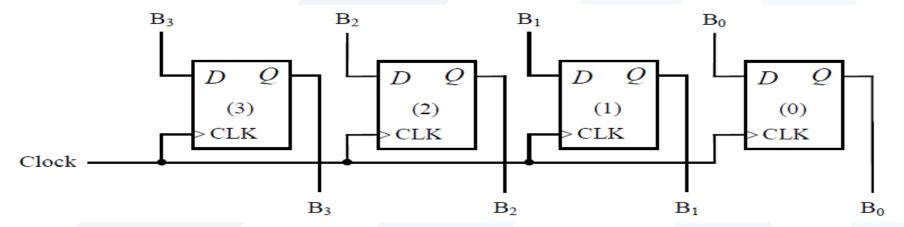

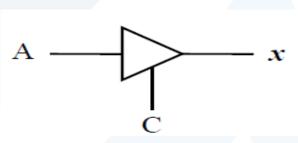

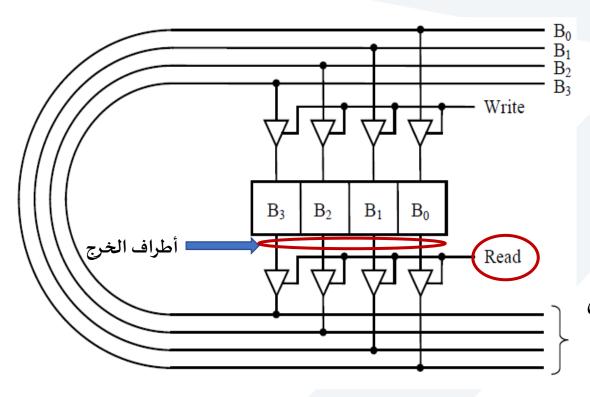

(4-bit Register) الشكل المجاور: يمثل المخطط المنطقي لمسجل مكونة من أربعة خانات

#### العمليات التي يمكن إجراؤها على المسجلات هي:

- ✓ الكتابة (Write): أي تخزين معلومة في المسجل

- ✓ القراءة (Read): أي استرجاع معلومة مخزنة في المسجل

- (Register-to-Register Transfer ) نقل ما بين المسجلات

حتبني المسجلات باستخدام القلاب D

خنحتاج إلى عدد من القلابات مساو لعدد الخانات الثنائية المطلوب تخزينها

مثال: الدارة المنطقية لمسجل مكون من أربع خانات ثنائية أي نحتاج إلى أربع قلابات D

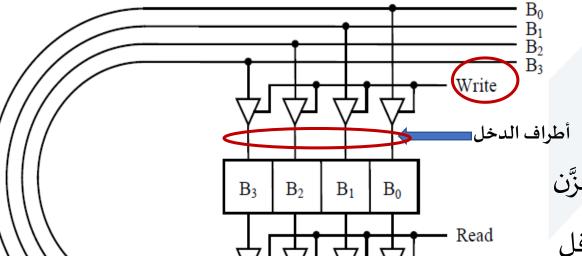

#### أطراف الدخل

#### أطراف الخرج

22

🔪 في إجرائية الكتابة:

تصل المعلومة المراد تخزينها عادة إلى المسجل من خلال ما يسمى ناقل بيانات (Data Bus) حفى إجرائية القراءة:

تنقل المعلومة المسترجعة من المسجل إلى الجهة المقصودة عبر ناقل البيانات

:Data Bus ناقل البيانات

عبارة عن مجموعة من الموصلات كل منها يحمل بت واحد فقط من البيانات.

مثال: ناقل بيانات ذو أربعة خانات

| $\mathrm{B}_{\mathrm{0}}$ | <br>)                     |

|---------------------------|---------------------------|

| $B_1$                     | (=1:1 . 151:              |

| $B_2$                     | ناقل بیانات<br>(Data Bus) |

| B <sub>3</sub>            |                           |

#### الكتابة في المسجلات والقراءة منها (٢/٤)

#### (Write and Read Operations)

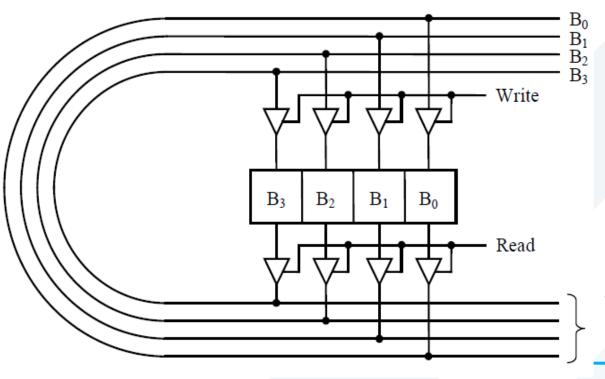

ربط كل من أطراف الدخل وأطراف الخرج للبيانات للمسجل بناقل البيانات باستخدام عوازل ثلاثية الحالة (buffers)

#### :(tristate buffer) العازل ثلاثي الحالة (\*

بوابة منطقیة لها طرف دخل A و طرف خرج x و طرف تحکم C

عندما C=1 يمر الدخل إلى الخرج X=A

عندما C=0 يعزل خرج البوابة عن دخلها وتسمى حالة المعاوقة العالية (High Impedance)

## الكتابة في المسجلات و القراءة منها (٣/٤) (Write and Read Operations)

#### 🗡 لإجراء الكتابة:

❖ نجعل إشارة 1= Write

- ✓ توصل أطراف الدخل للمسجل مع الناقل

- ✓ تنتقل البيانات الموجودة على الناقل إلى داخل المسجل و تُخزَّن

- ✓ من ثم توضع Write=0 لفصل أطراف الدخل عن الناقل ليصبح الناقل خالياً ومتاحاً لعمليات أخرى

### الكتابة في المسجلات و القراءة منها (٤/٤) (Write and Read Operations)

#### لإجراء القراءة:

- 💠 نجعل إشارة 1= Read

- ✓ توصل أطراف الخرج للمسجل مع الناقل

- ✓ تظهر البيانات المخزنة في المسجل على الناقل و تكون

متاحة لقراءتها من الناقل من قبل أية جهة طالبة لها

- ✓ من ثم توضع 0=Read لفصل أطراف الخرج عن للمسجل

عن الناقل. ليصبح الناقل خالياً ومتاحاً لعمليات أخرى

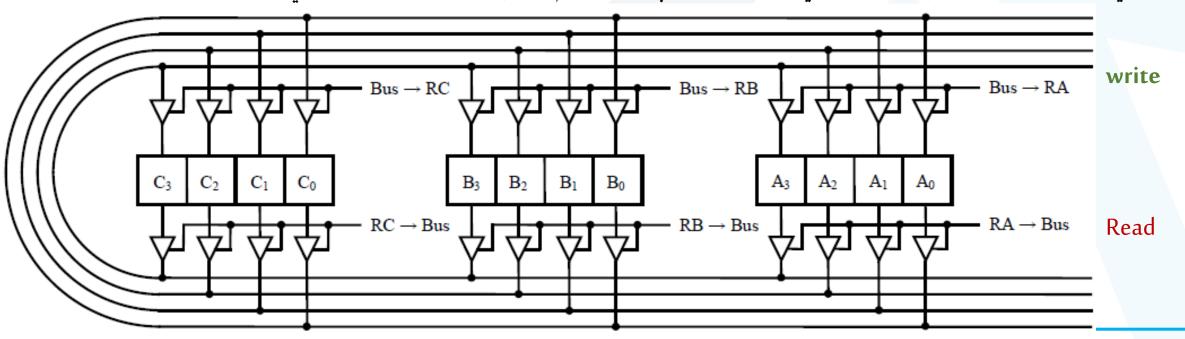

#### نقل البيانات بين المسجلات (١/٢)

#### (Register to Register Transfer)

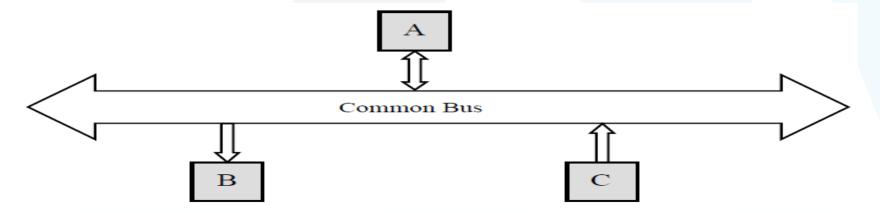

- ✓ لنقل البيانات بين مجموعة من المسجلات تربط تلك المسجلات بناقل مشترك ( Common Bus )

- ✓ يستخدم الناقل كوسيط لنقل البيانات من مسجل إلى آخر

- ✓ تُقرأ محتوبات المسجل الأول لتظهر تلك المحتوبات على الناقل وبعد ذلك يتم قراءتها بواسطة المسجل الثاني

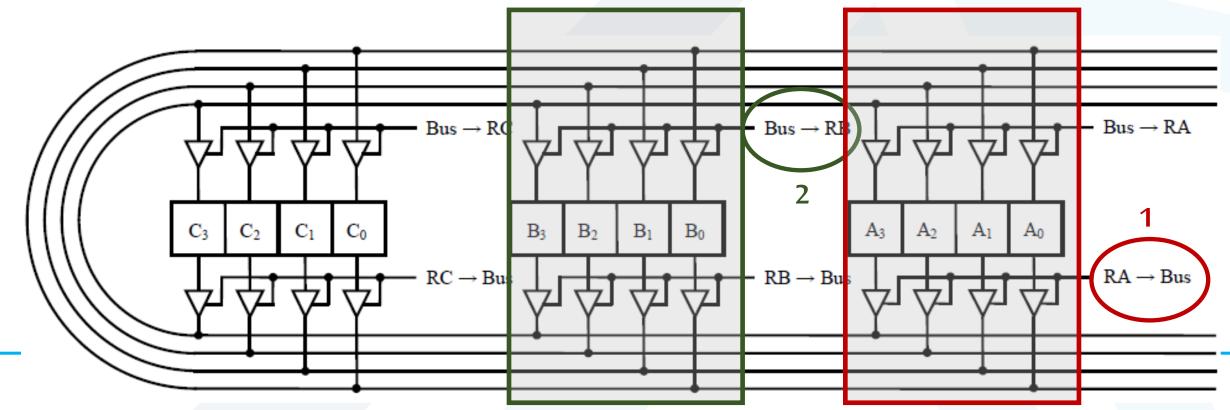

#### √ مثال: لإجراء عملية نقل البيانات RA → RB أي نسخ محتويات المسجل RA للمسجل RB للمسجل RB المسجل RB المسجل المس

- ا. نجعل الإشارة BUS → RA مساو لـ 1 فتظهر محتويات المسجل RA على الناقل (read)

- ۲. نجعل الإشارة BUS→RB مساو لـ 1 فتنتقل البيانات الظاهرة على الناقل إلى المسجل RB(write)

- $^{\circ}$  . نعيد الإشارتين $BUS \longrightarrow RB$  و  $BUS \longrightarrow RB$  إلى قيمة ، مرة أخرى لإخلاء الناقل.

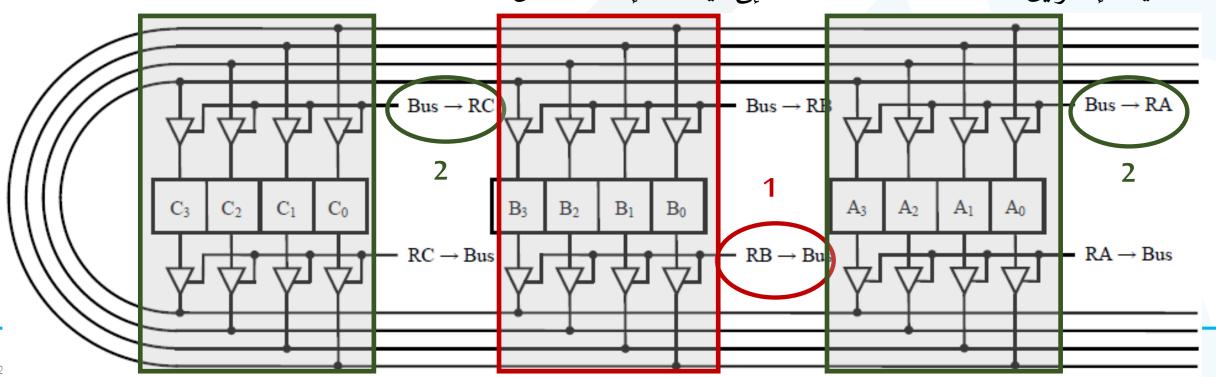

RA و RC أي نسخ محتويات المسجل RB للمسجلين  $RB

ightharpoons \{RA \ RC \ RC \}$  و RC مثال: لإجراء عملية نقل البيانات  $RB

ightharpoons \{RC \ RC \ RC \ RC \}$

ا. نجعل الإشارة BUS→Bus مساول 1 فتظهر محتويات المسجل RB على الناقل

٢. نجعل الإشارتين BUS→RC, BUS→RA مساوتين لـ 1 فتنتقل البيانات الظاهرة على الناقل إلى المسجلين RC وRC

الى قيمة ، لإخلاء الناقل BUS $\rightarrow$ RC, BUS $\rightarrow$ RA الناقل بعيد الإشارتين

#### نقل البيانات بين المسجلات (٢/٢)

#### (Register to Register Transfer)

الشائع في الأنظمة الرقمية استخدام ناقل مشترك لنقل البيانات بين الأجزاء المختلفة في النظام الرقمي

عرض الناقل المشترك من العوامل الهامة في تحديد سرعة عمل النظام الرقمي

كلما ازداد عرض الناقل كان من الممكن نقل كمية أكبر من البيانات عبره في عملية النقل الواحدة

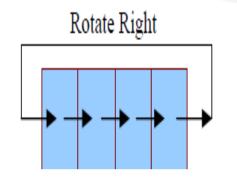

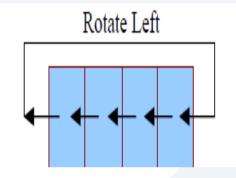

#### 🗡 مسجل الإزاحة:

عبارة عن مسجل يستطيع إضافة إلى العمليات السابقة ، عمل إزاحة للبيانات الموجودة بداخله بمقدار خانة واحدة أو أكثر يميناً أو يساراً .

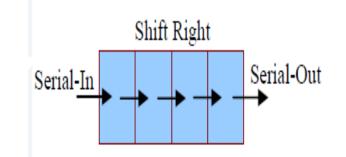

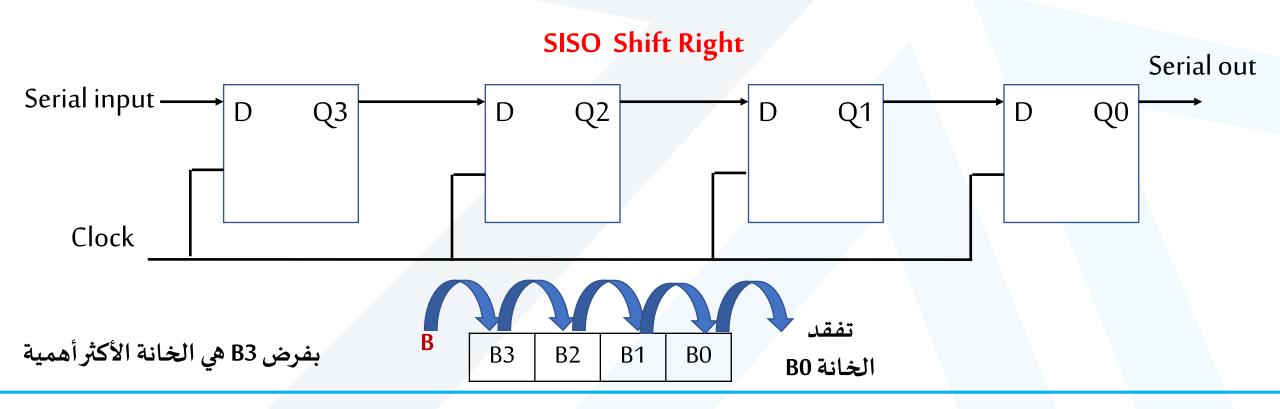

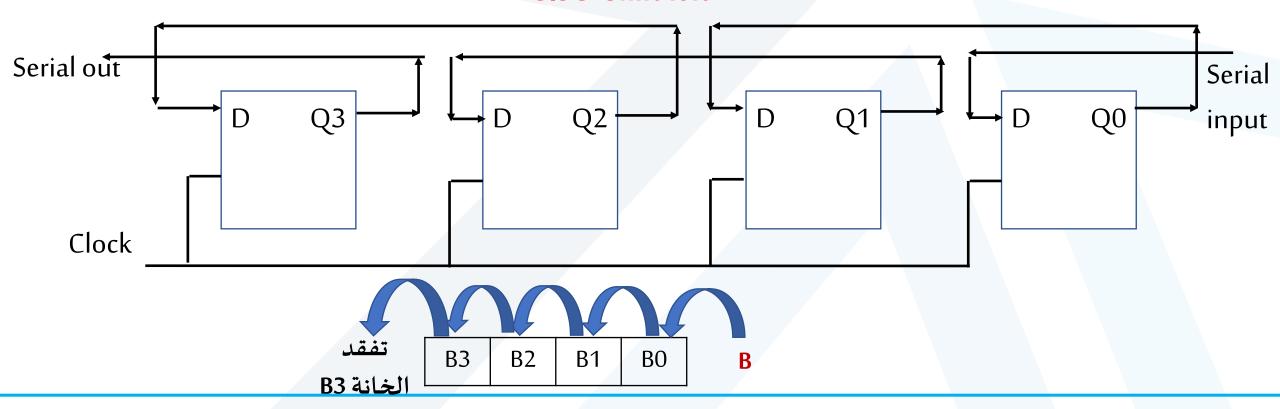

🗘 مسجل إزاحة دخله تسلسلي و خرجه تسلسلي (Serial in –Serial out SISO).

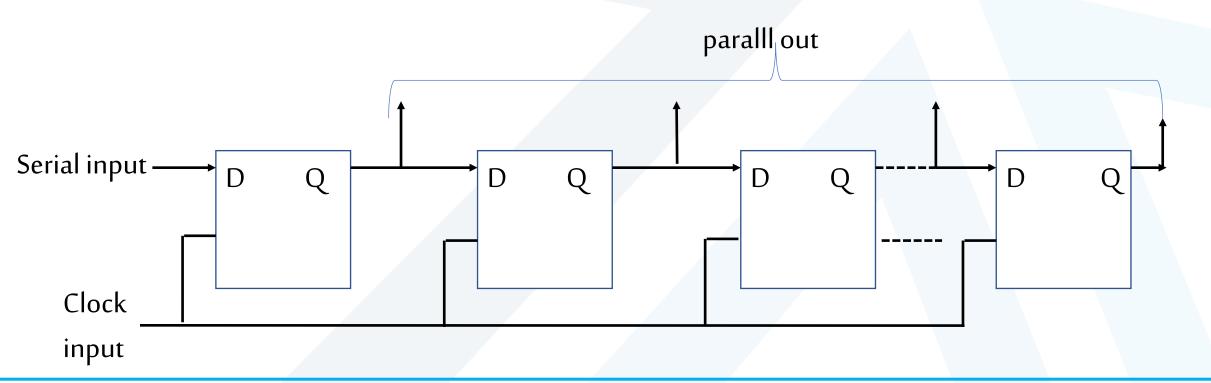

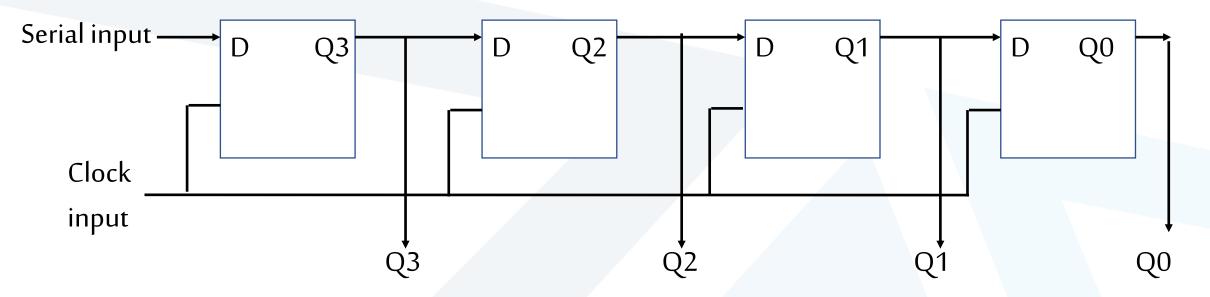

مسجل إزاحة دخله تسلسلي و خرجه على التوازي (Serial in –Parallel out SIPO).

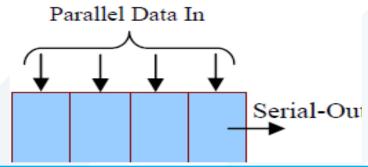

مسجل إزاحة دخله على التوازي و خرجه على التسلسل (Parallel in –Serial out PISO).

## مسجل إزاحة دخله تسلسلي وخرجه تسلسلي (SISO)

(Serial in —Serial out Shift Registers)

## مسجل إزاحة دخله تسلسلي وخرجه تسلسلي (SISO)

(Serial in —Serial out Shift Registers)

#### SISO Shift left

## مسجل إزاحة دخله تسلسلي وخرجه تسلسلي (SISO)

(Serial in —Serial out Shift Registers)

| clock | input | Q3 | Q2 | Q1 | Q0 |

|-------|-------|----|----|----|----|

| -     | -     | 0  | 1  | 1  | 0  |

| 1     | 1     |    |    |    |    |

| 2     | 0     |    |    |    |    |

| 3     | 0     |    |    |    |    |

| 4     | 1     |    |    |    |    |

﴿ بفرض لدينا مسجل إزاحة نحو اليمين مكون من ٤ خانات أي سيكون لدينا أربع قلابات من النوع D

بفرض أن القيمة المخزنة بالمسجل (الابتدائية) هي 0110 البيانات المراد تخزينها 1001 (Input)

كيف تتم عملية التخزين؟

#### مسجل إزاحة دخله تسلسلي و خرجه تسلسلي (SISO)

#### (Serial in -Serial out Shift Registers)

مع نبضة التزامن الأولى سيحدث إزاحة بمقدار خانة واحدة إلى اليمين للبيانات المخزنة داخل المسجل و في نفس الوقت الخانة الأولى من المسجل البيانات المراد تخزينها ستحدث لها إزاحة داخل الخانة الأولى من المسجل

| clock | input | Q3 | Q2 | Q1 | Q0 |

|-------|-------|----|----|----|----|

| -     | -     | 0  | 1  | 1  | 0  |

| 1     | 1     | 1  | 0  | 1  | 1  |

| 2     | 0     | 0  | 1  | 0  | 1  |

| 3     | 0     | 0  | 9  | 1  | 0  |

| 4     | 1     | 1  | 0  | 0  | 1  |

مع نبضة التزامن الثانية سيحدث إزاحة بمقدار خانة واحدة إلى اليمين للبيانات داخل المسجل و في نفس الوقت الخانة االثانية من البيانات المراد تخزينها ستحدث لها إزاحة داخل الخانة الأولى من المسجل

- مع نبضة التزامن الثالثة سيحدث إزاحة بمقدار خانة واحدة إلى اليمين للبيانات داخل المسجل و في نفس الوقت الخانة الثالثة من البيانات المراد تخزينها ستحدث لها إزاحة داخل الخانة الأولى من المسجل

- مع نبضة التزامن الرابعة سيحدث إزاحة بمقدار خانة واحدة إلى اليمين للبيانات داخل المسجل و في نفس الوقت الخانة الرابعة من البيانات المراد تخزينها ستحدث لها إزاحة داخل الخانة الأولى من المسجل

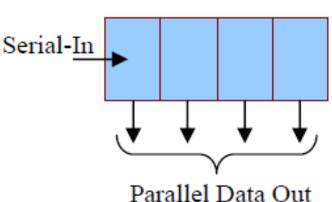

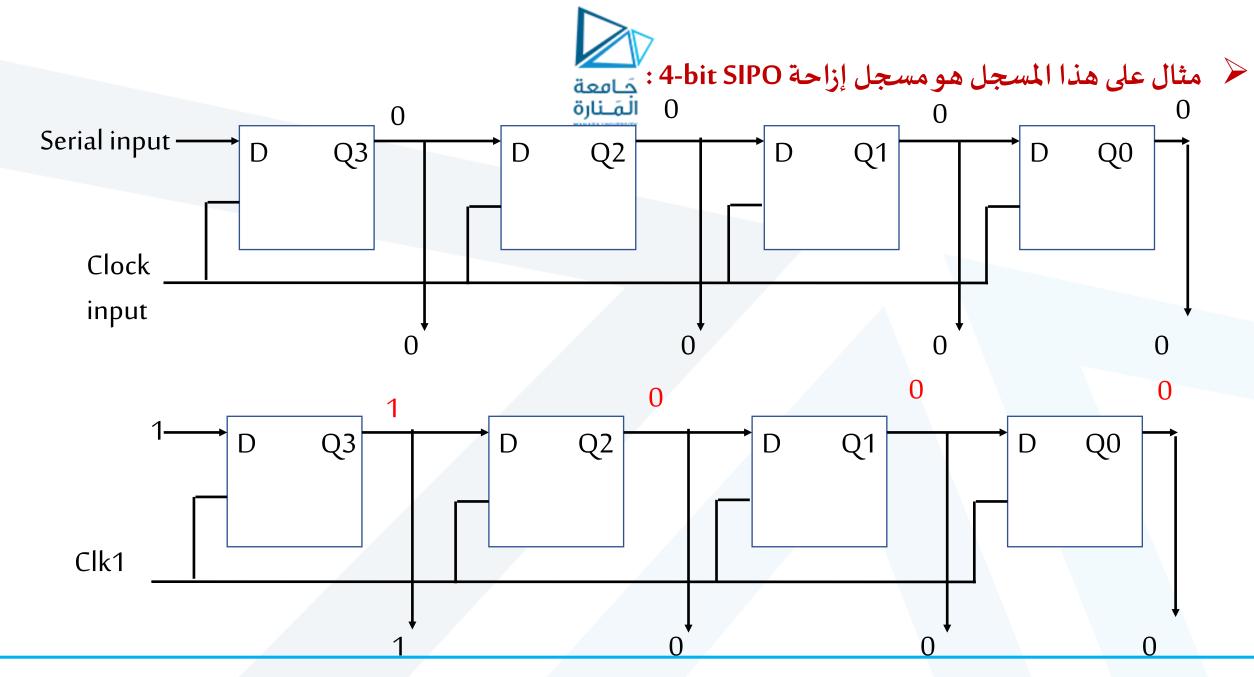

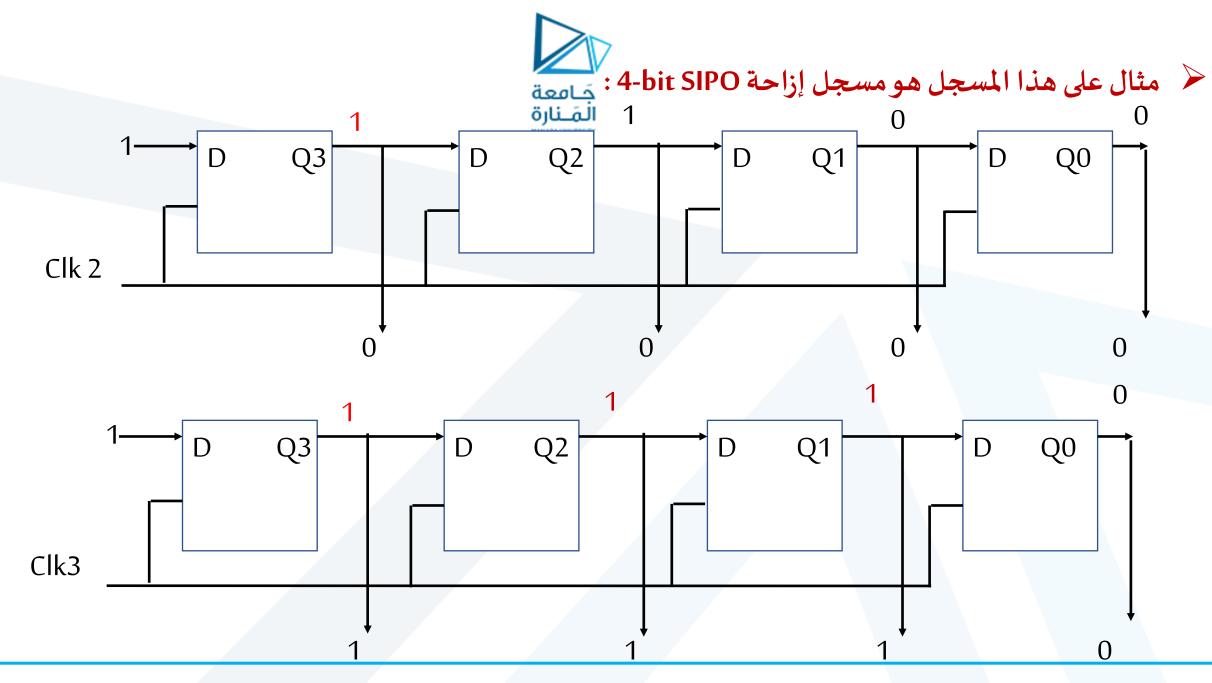

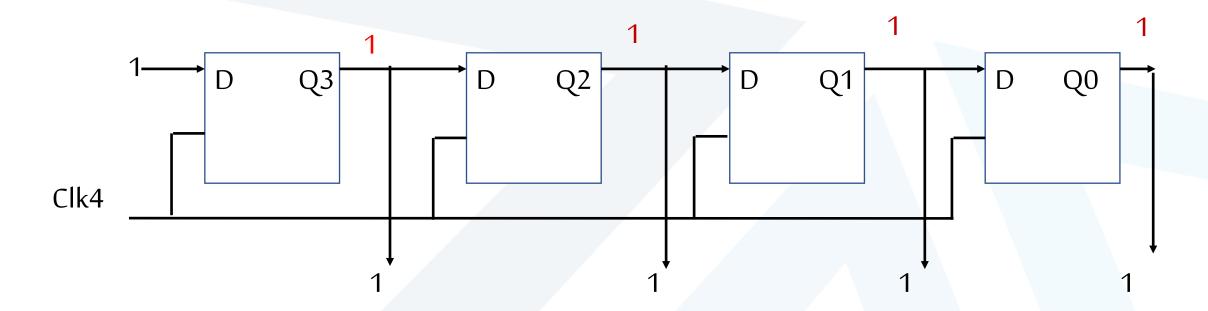

#### مسجل إزاحة دخله تسلسلي و خرجه على التوازي (Serial in –Parallel out Shift Registers SIPO)

﴿ هو مسجل إزاحة تدخل إليه البتات الواحدة تلو الأخرى أي تسلسلياً لكن تظهر على الخرج بشكل متوازي

مسجل إزاحة دخله تسلسلي و خرجه على التوازي (Serial in –Parallel out Shift Registers SIPO)

التحويل دخل من دخل تسلسلي بطول n بت إلى خرج متوازي يتطلب nنبضة ساعة لتحميلها.

← مثال على هذا المسجل هو مسجل إزاحة 4-bit SIPO:

تكون هذا المسجل من 4 قلابات نوع D بحيث خرج القلاب الأول هو دخل للقلاب الثاني و كل القلابات متزامنة مع بعضها كونها تستخدم إشارة تزامن واحدة

### مسجل إزاحة دخله تسلسلي و خرجه على التوازي (Serial in –Parallel out Shift Registers SIPO)

| clock | Q3 | Q2 | Q1 | Q0 |

|-------|----|----|----|----|

| -     | 0  | •  | •  | 0  |

| 1     | 1  | •  | •  | 0  |

| 2     | 1  | ١  | •  | •  |

| 3     | 1  | ١  | ١  | •  |

| 4     | ١  | ١  | ١  | ١  |

لإدخال أو تخزين كلمة مكونة من أربع بتات على التسلسل نحتاج إلى أربع نبضات تزامن . البيانات المخزنة داخل مسجل الإزاحة تكون على المخارج الأربعة Q0,Q1,Q2,Q3 كأربع بتات خرج على التوازي

### > مثال على هذا المسجل هو مسجل إزاحة 4-bit SIPO :

## نهاية المحاضرة الثامنة